基于SJA1000 IP核的CAN总线通信系统

(3)位数据流处理器程序

位数据流处理器程序执行总线上的错误检测、仲裁、填充和错误处理等功能。它主要由接收模块、发送模块、错误管理模块、CRC校验、验收滤波、FIFO6个子模块组成。CRC校验、验收滤波、FIFO子模块将单独设计成子程序供位数据流处理器程序调用。

(4)CRC校验程序

CRC校验程序主要用来完成CAN总线网络中循环冗余校验码功能。

(5)验收滤波器程序

验收滤波器程序的功能是由验收代码寄存器(ACR)和验收屏蔽寄存器(AMR)共同完成的。验收代码寄存器将接收到帧中的标识码内容与其自身的内容逐位的进行比较,以决定是否要接收这条报文,验收完全通过后则保存到FIFO中。验收屏蔽寄存器则决定在比较中起作用的验收代码寄存器的位(验收屏蔽寄存器为0,则相应的验收代码寄存器的位相关;验收屏蔽寄存器为1,则对应的位无关)。

(6)先入先出FIFO存储器程序

先入先出FIFO存储器程序的功能是先对接收的报文进行存储,并在CPU要求读出数据时,将接收到的数据通过数据总线从控制器中读出。FIFO模块特点是先进入先输出,后进入后输出。本文中的FIFO存储器是同步的,只有一个时钟信号。

(7)顶层控制程序

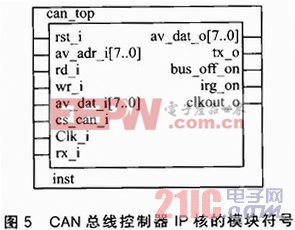

顶层控制程序(can_top)是整个CAN总线控制器SJA1000 IP核的最上层模块,主要负责调用并控制以上6个程序模块协同工作。

程序全部设计完后,通过使用QuartusII9.0的编译和综合将整个程序封装成模块符号的形式,如图5所示。这样方便存后面的CAN总线通信系统设计中调用。本文引用地址:http://www.eepw.com.cn/article/154098.htm

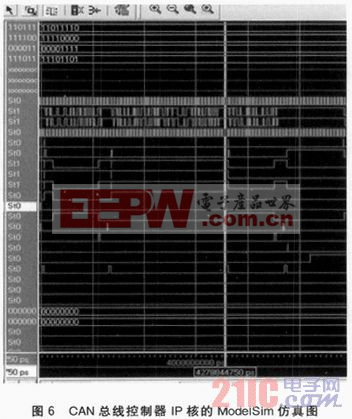

对CAN总线控制器IP核的仿真是在ModelSim软件测试平台中进行的,其仿真结果如图6所示。

从图6中我们可以得出:白色竖线处发送成功状态(tx_successful)置1,竖线前面一段时间内,CAN总线控制器IP核的发送状态(transmit _status)为1,接收状态(receive_status)为0,这说明控制器前面已成功地完成了一次发送操作;随后硬同步(hard_sync)置1,发送状态为

0,接收状态为1,控制器又开始一次接收操作,并在接收完后发送应答位(send_ack置1),且置info_empty为1。

3 SJA1000 IP核的CAN总线通信系统设计

基于SJA1000 IP核的CAN总线通信系统是将8051IP核、数据RAM、程序ROM以及CAN总线控制器IP核一同设计到FPGA芯片内,从而构成SPOC系统的。基于IP核复用技术的CAN总线硬件连接图如图7所示。和传统的CAN总线系统构架不同,本文的设计采用的是FPGA而不是单片机作为CAN总线通信系统的控制器。相对于单片机等微处理器而言,FPGA有着其独特的优势:I/O口资源丰富,可以很容易地实现更多的扩展功能;而且在电路设计中除了极少数必要的外围器件外,其余的电路都可以集成设计到FPGA中。这样做可以减少由于器件较多而产生的电磁干扰的可能性,而且还可以减少系统的体积和功耗、提高系统的可靠性。

在CAN 2.0B协议中,为了能够达到设计透明度以及实现灵活性,根据ISO/OSI参考模型,CAN被细分为以下不同的层次:

①数据链路层。其中包括逻辑链路控制子层(LLC)和介质访问控制子层(MAC)。

②物理层。物理层的作用是在不同节点之间根据所有的电气属性进行位的实际传输,它是由CAN总线驱动器和电气线路构成的。

逻辑链路控制子层(LLC)和介质访问控制子层(MAC)的功能,即报文分帧、仲裁、应答、错误检测和标定、报文滤波、过载通知以及恢复管理都是由CAN总线控制器实现。因此,CAN总线控制器IP核(CAN_Module)主要完成LLC和MAC子层的功能。

4 CAN总线通信系统的测试与验证

4.1 硬件电路的设计

CAN总线SOPC硬件连接图如图7所示,下面对图7所示的两个部分进行简单介绍。

4.2 系统的控制部分

控制部分选用的是KX_7C5E型实验电路板,该实验板中的FPGA目标芯片是Altera公司的Cyclonc III型EP3C5E144C8。其中FPGA芯片包含有8051单片机IP核、CAN总线控制器IP核、内部程序ROM、内部数据RAM和锁相环(PLL)等模块。

4.3 CAN总线收发器部分

因为FPGA芯片的供电电压和I/O口输出电平为+3.3 V,所以在设计中CAN总线收发器选用的供电电压也必须是3.3 V的。CTM1050T CAN总线收发器模块是集成电源隔离、电气隔离、CAN总线收发器和CAN总线保护于一体的CAN总线隔离收发器模块。有了CAN总线隔离收发器,就可以很好地实现CAN总线上各节点电气、电源之间的完全隔离和独立,这样可以提高各个节点的稳定性和安全性。该模块的TXD、RXD引脚不需要外接其他元器件就可以很好地兼容+3.3 V及+5 V的CAN总线控制器。因此在图7中我们将FPGA的I/O口与CTM1050T的引脚直接相连,故没有设计任何外围电路。

最后通过使用KX_7C5E型实验电路板、CAN总线收发器、USBCAN-II、CAN总线实验台实验,能够进行基本的收发,验证了系统的可行性。

结语

本文已成功验证了基于SJA1000 IP核的CAN总线通信系统的可行性,该设计充分展现了片上可编程系统的灵活性和可移植性,减小了系统体积和功耗,完全可以代替原有传统的CAN总线系统方案。

评论