基于MC8051软核的星载智能1394终端

1引言

本文引用地址:https://www.eepw.com.cn/article/152639.htmIEEE1394是一种高速串行总线,它最初是由Apple公司与20世纪80年代中期开发的FireWire总线。1995年,IEEE制定并颁布了IEEE 1394-1995标准,并在2000年推出了IEEE 1394a标准,可以支持100Mbps、200Mbps和400Mbps的传输速率。在最新的IEEE1394B标准中,支持的传输速率提高到了800Mbps、1.6Gbps和3.2Gbps。IEEE1394总线以其高传输速率的特点已经在视频传输、网络互联及计算机外设等领域有了广泛的应用[1]。目前在航空[2]及航天应用中对大量数据的高速实时传输要求不断提高,IEEE1394具有数据传输速率高、支持等时传输等特点,因而成为未来星载数据总线的选择之一。

在星载应用中,由于任务的多样性,对星载总线接口的需求多种多样。譬如部分载荷本身没有集成1394接口却需要用1394总线来传输数据;或者几个载荷需要共用一个1394总线接口;或者是载荷自身没有带微控制器等控制单元。并且各种载荷对外的数据接口也是各不相同的。这时就需要一种体积小,简单并且易于扩充接口能的智能终端配合载荷一起工作。由于IEEE1394总线协议比较复杂,实际应用中大多数采用专用的1394总线芯片,面向专用系统的1394芯片都支持微处理器接口。常见的1394总线设计采用的是微处理器加上1394总线芯片及外围逻辑芯片,这种设计方案需要的芯片数量多,接口设备体积大,扩充接口功能实现起来比较复杂。

针对IEEE1394星载应用的实际需要,本文基于MC8051软核,提出一种简单、低功耗、小型化和易于扩展的IEEE1394智能终端设计方案,克服了以往1394总线接口硬件电路复杂、使用芯片多、体积大等缺点,并且可以很方便地扩展接口的其他功能。

2 系统实现方案

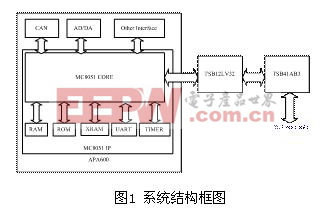

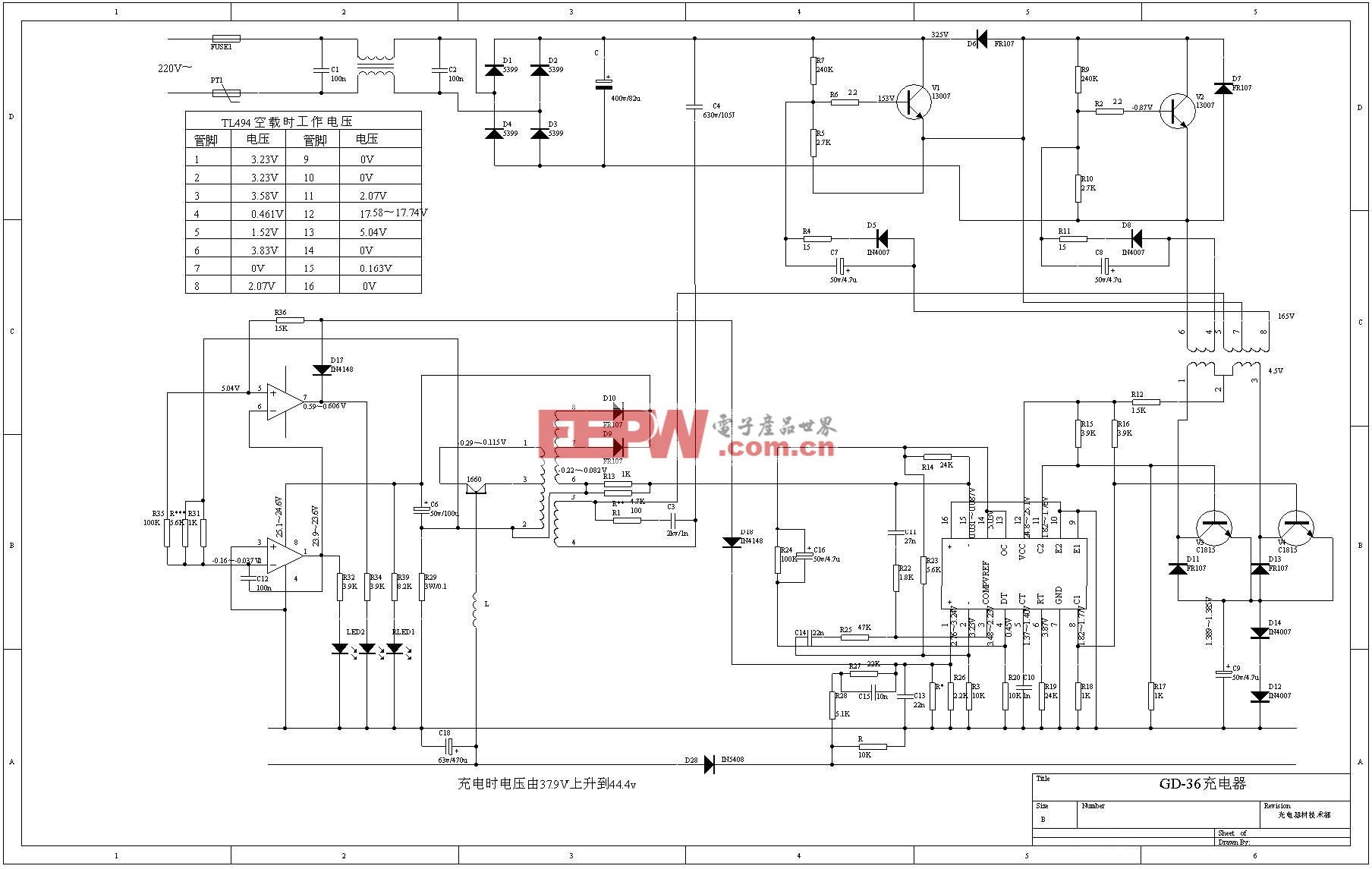

整个1934接口系统的框图如图1所示。采用的是Actel公司基于FLASH技术的ProASIC Plus系列FPGA芯片APA600。它具有单芯片上电即用、高性能和低功耗等特点[2]。由于上电即用,减小了电路板体积,有助于简化电路设计。在方案试验中使用的是TI公司的链路层芯片TSB12LV32[3]和物理层芯片TSB41AB[4]。TSB12LV32是一款高性能的通用IEEE1394a链路层芯片,用于在主控制器和1394物理层芯片以及连接到链路层DM口的外部设备之间的数据传输。它兼容IEEE1394-1995和P1394a标准,支持400、200和100Mbps的传输速率。提供可选的具有多种操作模式的8位/16位微控制器接口,最大支持60MHz。芯片内部分别内置了2K字节大小的通用接口FIFO和异步传输FIFO,用于微控制器接口和物理层接口之间的数据包传送,8位/16位数据移动端口支持25MHZ下的等时、异步和数据流包的发送和接收。TSB41AB3是一款三端口兼容IEEE 1394-1995和P1394a标准400Mbps的物理层芯片.

在FPGA中整合了开源的兼容标准8051的微控制器IP核MC8051,将程序存储器、程序存储器、外部数据存储器以及UART和定时器都集成在一片FPGA中。可以根据任务需要很方便地在FPGA内定制其他所需要的接口和逻辑单元,譬如AD/DA控制,CAN总线等。

通过上述三个部分可以构成面向特定应用的完整的1394总线接口系统。

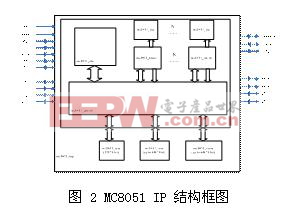

3.1 Oregano Systems MC8051 IP Core¬[5]

Oregano Systems公司发布的MC8051 IP Core是一个基于GUN LGPL的开源IP Core。它完全兼容标准的8051控制器,并且对其体系结构作了改进,在使用相同时钟频率情况下,将指令的执行时间下降到1到4个时钟周期,因此速度得到了十几倍的提升,并且降低了功耗。MC8051模型是可综合RTL风格,完全的同步设计,具有单一时钟网络,通过调整和修改VHDL代码可以轻松地扩展其功能。具有128字节的片内RAM,最高可以支持64K的ROM和RAM,并且集成了UART、定时器、中断和4组8位的I/O口。

3.2 MC8051设计要点

评论