短波通信中一种时延设计方法与DSP实现

从图4可以看出,在输入信号x(n)经过40倍内插滤波器滤波,并进行40倍抽取实现后的输出信号与输入信号有着相同的时域波形,并且输出信号时域波形相对输入信号时域波形出现了相应的延时。本文引用地址:http://www.eepw.com.cn/article/152188.htm

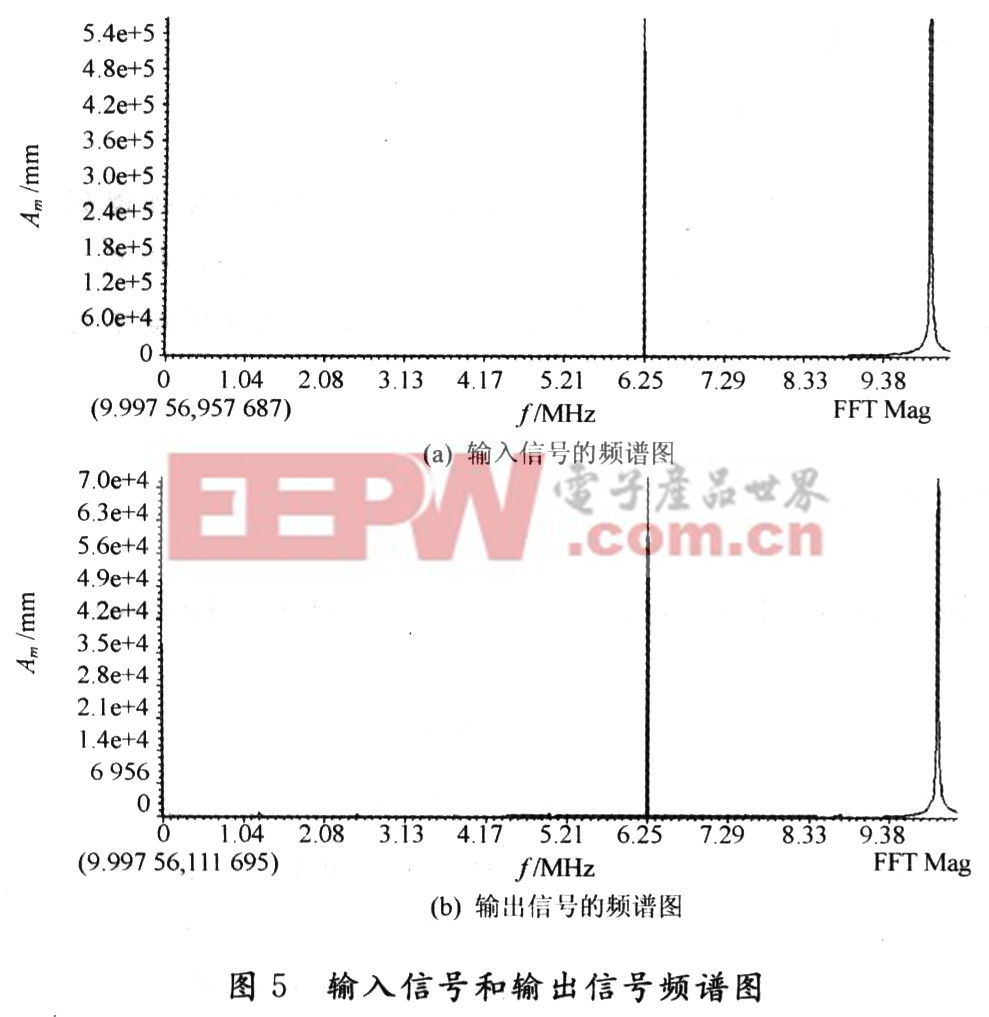

图5为输入、输出信号的频谱图。

在原始采样频率fs为25 MHz下,输入信号x(n)经过40倍内插滤波器滤波并进行40倍抽取实现后,对输入输出进行频谱分析,可以得出输出信号的采样频率仍是25 MHz,并含有两个频率信号,其一信号频率f1=6.25 MHz,另一信号频率f2=10 MHz。从而得出输出信号频谱与输入信号频谱是吻合的,如图5所示。

3 结语

提出了一种实现时延的方法。可以选用大容量存储器作大尺度的延时处理,并选用DSP作插值算法做高精度的小尺寸的延时算法处理。结合软件无线电思想中的内插和抽取技术,重点介绍高精度、小尺寸的信号延时处理方法。它具有DSP处理时间周期短,节省DSP数据存储空间,时延精度高等特点。用实验板SEED-DEC6416进行硬件仿真。试验结果表明,设计结果基本达到要求,该方法的实现过程是可行的。

评论