利用FPGA来实现RC6算法的设计与研究

式中:e一2.782 818 284 59…(自然对数);φ=1.618 033 988 749…(黄金分割)

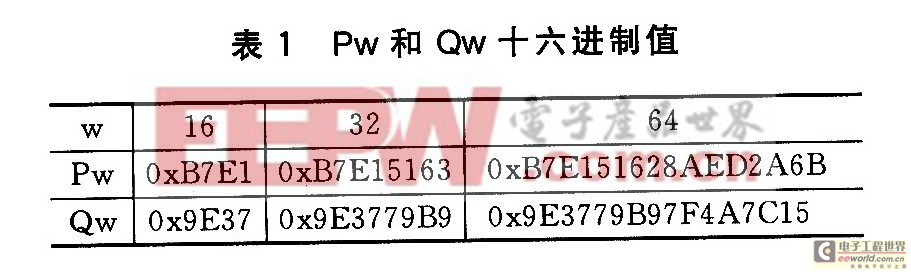

当w分别为16、32、64时,常数Pw、Qw分别如表1所列。在本设计中,w=16,输入为128位的主密钥,得到的是44个32位子密钥。

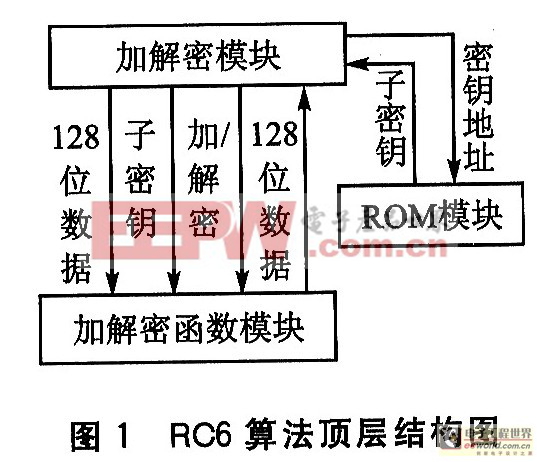

RC6协处理器包含以下3个模块:加解密模块,加解密函数模块和ROM模块。顶层结构如图1所示。

加解密模块:包括输入和输出、加/解密选择、状态机,以及函数调用声明和ROM调用取址。用于输入128位明文或密文,并且利用一个状态机定义程序顺序执行和保证循环控制,实现对ROM的44个子密钥读取,以及将数据输入函数中进行处理。由于输入ROM的地址是在一个时钟控制下,子密钥数据的输出有一定的延时,所以利用一个控制变量cnt实现地址提前一个时钟左右输入ROM,ROM接收到后输出子密钥,使在进行数据加解密处理时,已经有准备好的子密钥调用。

加解密函数模块:利用work用户自定义函数库,定义算法中用到的函数。其中包括5个函数,分别是:RFunct、afunct、cfunct、lshift、rshift。顶层文件循环调用此函数21次,进行加解密运算。

ROM模块:先在QuartusII里面将预定义的子密钥输入rc6keyrom.mif文件中,调用QuartusII的MegaWizardPlug—In Manager,自动生成ROM,供顶层文件调用。需要提前利用QuartusII建立一个.mif文件,将子密钥的数据输入。

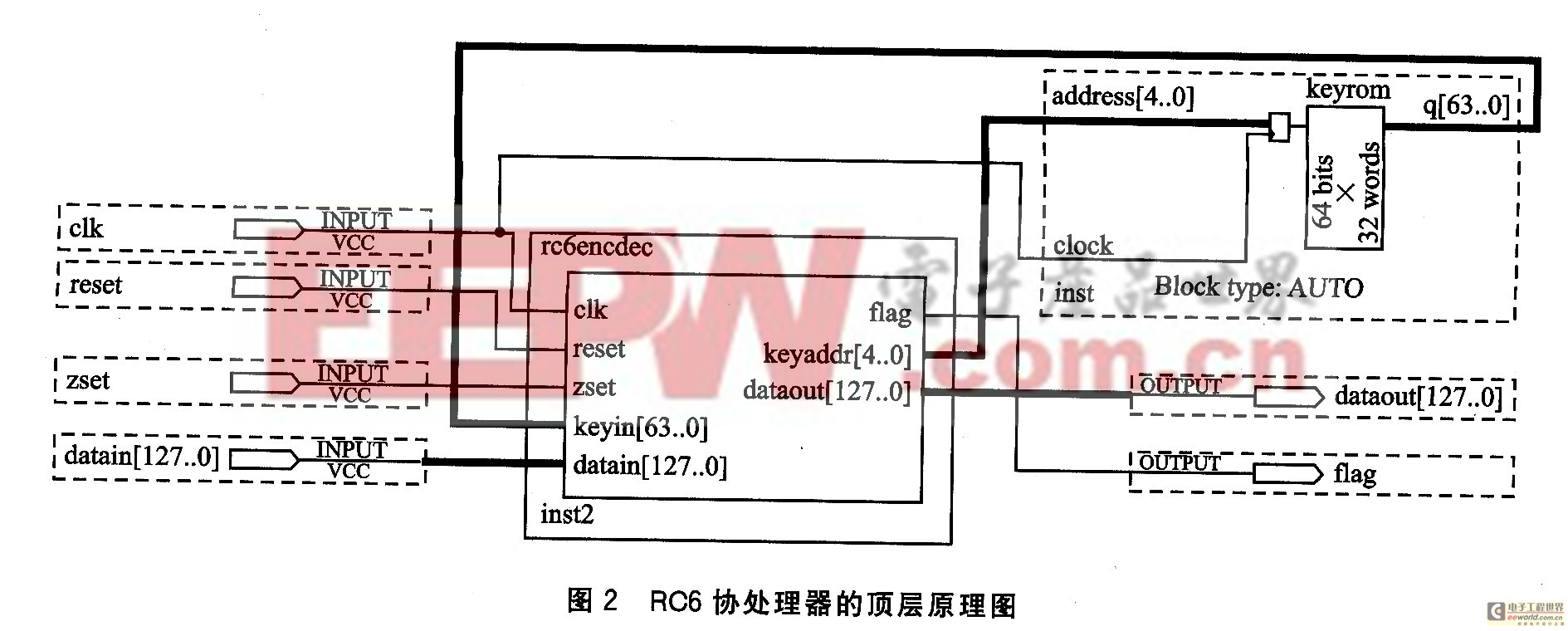

2.2 RC6协处理器的顶层原理图

如图2所示,基于FPGA的RC6算法协处理器分3个模块:顶层模块、RC6加解密函数模块和ROM模块。共有260个I/0口,包括131输入端口和129个输出端口。

2.3 各模块的功能及实现

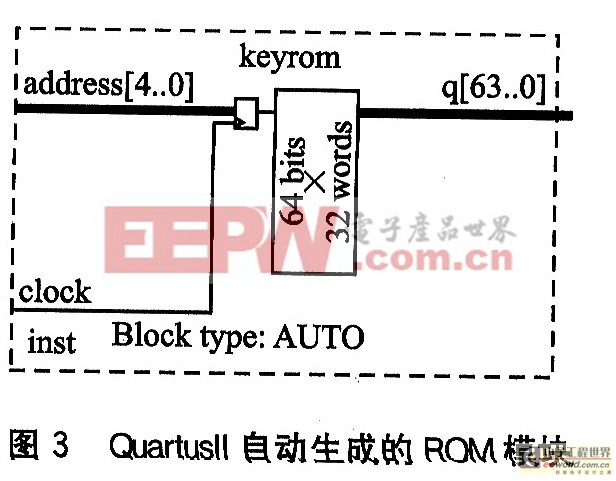

2.3.1 ROM模块

图3为QuartusII自动生成的ROM模块。ROM取址需要由加解密模块提供地址输入,然后输出子密钥。输入地址为address[4..0],输出为q[63..0]两个子密钥一起输出到主程序中进行。

评论