基于PicoBlaze软核的TFT液晶显示控制

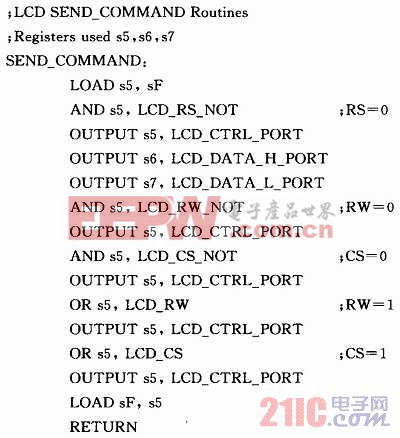

其中,delay_lus_constant=(clock_rate-6)/4,这里clock_rate为50。实现了端口位操作和软件延时功能,即可按照8080并行读写时序编写发送命令子程序。其程序代码如下:

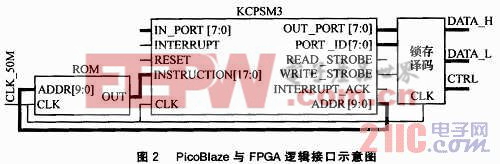

3.2 PicoBlaze与FPGA的逻辑接口

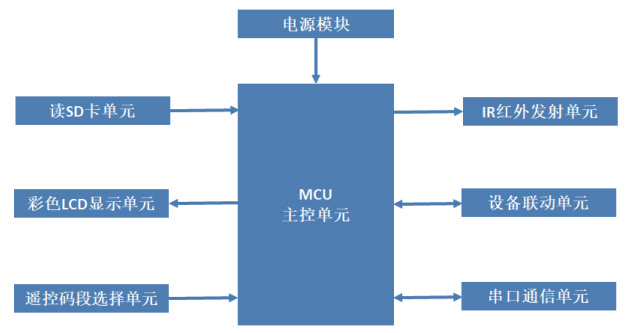

PicoBlaze与FPGA的逻辑接口主要在FPGA逻辑设计中例化PicoBlaze单元,将其与程序ROM相连,并完成输入、输出端口的锁存译码。其接口示意图如图2所示。本文引用地址:http://www.eepw.com.cn/article/150935.htm

PicoBlaze的汇编程序经汇编工具KCPSM3.exe编译后,将其程序代码填充到由BLOCK RAM组成的程序ROM中,在FPGA逻辑设计中,将程序ROM和PicoBlaze模块KCPSM3的对应引脚相连即可。锁存译码单元在每个有效时钟沿,在WRITE_STROBE的使能控制下对PORT_ID进行译码,并将OUT_PORT上的数据锁存到相应的寄存器中。本设计包含3个端口,分别是数据线高8位DATA_H、数据线低8位DATA_L和控制线CTRL,其中CTRL的bit0~bit4分别表示RS、RD、RESET、WR和CS。

在FPGA逻辑中完成PieoBlaze的例化和相关逻辑设计后,即可用Xilinx的集成开发工具ISE进行综合、实现和下载验证。综合结果显示,本设计共占用了102个Slice和1个RAMBl6S单元,仅占XC2VP30-7FF896总Slice数和BRAM单元的1%。最后,将生成的比特流下载到Xilinx XUP Virtex-II PRO开发板上进行验证。结果表明,能够正确驱动TFT液晶显示单种或多种颜色,达到了预期目标。经测算,当系统时钟为50 MHz时,全屏刷新一次约需55.4 ms,具有较高的实时性。如果将系统时钟提高到100 MHz,还可以进一步加快刷新速度。

结语

本文设计的基于PicoBlaze软核的TFT液晶显示控制方案,已在XilinxXUP Virtex-II PRO开发板上进行了验证,取得了良好的效果。通过本设计方案可以看出,PicoBlaze是一个功能强大、应用灵活的8位嵌入式软核处理器,可用于实现非关键时序的复杂控制功能,而其他关键时序和数据通道功能则需FPGA逻辑来实现,二者有机结合将使得系统设计更加方便、灵活。

评论