用VHDL设计有限状态机的方法

end if;

end process state_clocked;

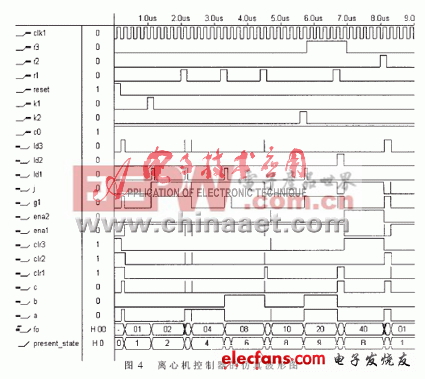

end state_machine;利用EDA软件MAX+plus Ⅱ对该程序进行编译、仿真,其仿真波形见图4。

从图4仿真波形图上可以看出,状态机的输出信号有许多“毛刺”产生。如何消除这些“毛刺”是下面将讨论的问题。

在同步电路中,一般情况下“毛刺”不会产生重大影响。因为“毛刺”仅发生在时钟有效边沿之后的一小段时间内,只要在下一个时钟有效边沿到来之前“毛刺”消失即可。但是,由于状态机的输出信号都是作为其它功能模块的控制信号,如果这些控制信号作为异步控制(如本系统中的CLR)、三态使能控制或时钟信号来使用,则将会使受控模块发生误动作,造成系统工作混乱。因此,在这种情况下必须保证状态机的输出没有“毛刺”。

消除状态机输出信号的“毛刺”有以下三种方案:

·在状态机输出信号较少的情况下,直接把状态作为输出信号;

·对于顺序迁移的状态机,选择雷格码作为状态编码;

·在Moore型或Mealy型状态机基础上,用时钟同步输出信号。

本设计采用后两种方案,较简便。雷格码的特点是:当状态机改变状态时,状态向量中仅1位发生变化。与前面用可枚举类型定义的状态变量不同,现在选用常数来指定各状态变量的取值为格雷码。修改部分设计程序如下:

若要完全消除状态机的“毛刺”,则应采用第三种方案。这时,设计程序要作相应改变,状态的转移和输出信号的赋值要写在同一个时钟进程中。

综上所述,采用VHDL设计状态机,能够大大降低设计难度。使用双进程描述风格编写VHDL设计程序,可以清楚地在一个进程中确定状态的转移和对输出的赋值,而且具有易于建立、理解和维护的优点。特别针对大型或具有大量状态转移和输出信号的状态机设计,将会更加显示出它的优势。对于状态机输出信号所产生的“毛刺”,可以按照系统的要求,根据不同的情况采用相应的设计方案予以消除

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论