一种DSP与PCI总线的接口设计

1 引言

本文引用地址:http://www.eepw.com.cn/article/150296.htm DSP+PCI数字信号处理方案可利用PC的强大功能实现对DSP的操作控制、数据分析和操作监视等。DSP+PCI方案能充分满足数字图像、语音处理、高速实时数据处理等领域的应用,为DSP系统的低成本实现提供了解决方案。

2 TS101S型DSP介绍

本系统采用美国Analog Device公司的

高性能TIGER SHARC 101S(简称TS101S)作为主处理器。TS101S处理器劫持32bit和64bit浮点,以及8、16、32和64bit定点处理。它的静态超量结构使其每周期能执行多达4条指令,进行24个16bit定点运算和6个浮点运行。其内部有3条相互独立的128bit宽数据总线,每条连接3个2Mbit内部存储块中的一个,提供4字节的数据、指令、I/O访问和14.4Gbyte/s的内部存储带宽。以300MHz时钟运行时,其内核指令周期为3.3ns。在发挥其单指令多数据特点后,TS101S每秒可以进行了24亿次40bitMAC运算或6亿次80bitMAC运算。以300MHz时钟运行时,完成1024点复数FFT(基2)仅需32.78μs,1024点输入50抽头FIR需91.67μs。TS101S有强大的链路口传输功能,每个链路口传输速度达到250Mbyte/s。总的链路数据率达1Gbyte/s(4个链路口),超过了外部口的传输速率(800Mbyte/s)。

3 PCI介绍

PCI(Peripheral Component Interconnect)总线是一种不依附于某个具体处理器的高性能局部总线,因此开发PCI设备可独立于处理器,具体由一个桥接电路(PCI桥)实现对这一层的管理,并实现上下之间的接口数据传送。可以把PCI桥描述为实现通用总线与PCI总线的地址映射、协议转换、数据缓存等功能的逻辑接口。

3.1 PCI桥的实现

开发者可以根据PCI总线规范所定义的电气特性、时序要求来进行接口设计。一种方式是使用可编程逻辑器件(FPGA/CPLD)根据实际需要的功能来设计,这种方式的成本低、灵活性高,但需要对PCI总线协议有充分的掌握,或者需要生产可编程逻辑器件的厂商提供PCI接口功能模块。由于PCI总线的规范较复杂,一般用户都会选择专用的PCI接口电路,无需详细理解底层的PCI总线协议,而只理解到应用层即可。因此,本文介绍的系统采用后一种方案,PCI接口电路采用现在市场上使用较普通的PLX公司的PCI9054。

3.2 PCI9054

PCI9054采用先进的PLX数据流水线结构技术,是32位、33MHz的PCI总线主I/O加速器,符合PCI本地总线规范2.2版,有M、C、J三种模式。针对不同的处理器及局总线特性可选,尽量减少中间逻辑;具有可选的串行E2PROM接口,本地总线时钟可和PCI时钟异步。PCI9054内部有6种可编程的FIFO,以实现零等待突发传输及本地总线和PCI总线之间的异步操作,支持主模式、从模式、DMA传输方式,功能强大,可应用于适配卡和嵌入式系统。

4 DSP+PCI应用实例

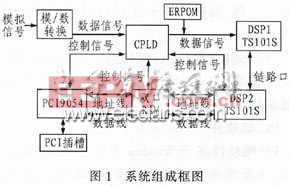

DSP+PCI数字信号处理系统的组成如图1所示。模块信号先输入模/数转换器,然后经过由CPLD锁存数据到DSP1,经链路口到DSP2,数据处理完后再通过PCI9054把数据传到PC。此外CPLD还作为PCI9054与TS101S的接口逻辑转换。采用PCI9054与单个TS101S之间放置双口RAM作为缓存的接口方式。DSP采用EPROM加载方案。

本系统的特点是以尽量简单的方式来实现系统功能,因此采用了DSP间链路的口互连方式,这样一来,每对链路口互连仅需10条信号线,而采用总线互连方式时需超过100条信号线,可大大简化PCB板的复杂度。二个DSP间保留2个链路通道,总数据速率可达500Mbyte/s。路口互连是ADSP系统的特有功能,也是ADSP处理器能以低成本组成多片高性能信号处理机的主要原因。

4.1 TS101S与PCI9054的接口

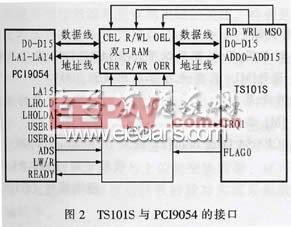

由于TS101S没有专门的PCI接口,而PCI9054也仅在M模式下才能实现与MPC850或Power QUICC等Motrola电路的无缝连接,因此,T

S101S与PCI9054之间需要可编程逻辑器件进行逻辑转换。出于对研制周期的考虑,采用一种较为简便的通信方式:在DSP与PCI桥间插入一个双口RAM,双口RAM一端的地址数据线接ISI101S,另一端的地址数据线接PCI9054。通过双口RAM转换数据,并作为公共访问缓冲区。这样,PCI桥与DSP之间的访问成为间接,可以大大削弹对PCI的时序要求,DSP与PCI之间只需少量的信号通过CPLD来实现逻辑转换,而无需总线仲裁,这种方式的时序简单,控制信号较少,DSP与CPLD编程简单,应用更为方便。双口RAM的型号为IDT70261,容量为16k×16bit。

PCI9054的工作方式为从模式,驱动方为PC,数字信号处理机作为LOCAL端的主机,中间由公用的双口RAM进行读写操作。在时序上,只需几个简单的控制信号进行握手即可实现双向数据传输。由PC主动发出读写命令,可根据需要实现单字节读写,在大多数系统中,这种方式已经满足要求。具体的接口电路如图2所示。

PIC9054局部总线侧的信号功能如下所述。

LHOLD:总线请求信号,由PCI9054驱动,高电平有效,有效时表明其正在使用本地总线。

LHOLDA:总线请求应答,由LOCAL端设备驱动,在LHOLD有效后一个周期有效,直至LHOLD无效后才无效,以向PCI9054表明LOCAL端未占用总线。

ADS:地址阈门信号,低电平有效,表明一个总线访问周期的开始,第一个时钟有效,持续一个LCLK,此后地址线有效。

USERo:用户输出信号,由PCI9054驱动,引入CPLD,作为DSP的外部中断请求。

USERi:用户输入信号,由外部设备驱动,PCI9054可查询到外部设备发出的信号。

LW/R:读写信号,由PCI9054驱动。

READY:从模式下为输入信号,当一个访问周期结束时,LOCAL端的设备要向PCI9054发出READY信号,表明完成本次访问,可开始下一轮访问。

4.2 系统工作方式

由于本系统采用RAM缓冲方式,因此PCI9054和DSP间只需握手信号即可。通过DSP的外部中断IRQ和标志引脚FLAG,以及PCI9054的用户输入/输出USERi/USERo相互配合实现握手,可实现基本的单字节读写,如果需要更复杂的功能,可以加上控制字来实现。地址映射是双口RAM的数据宽度为16位,PCI9054地址的LA1-LA14分别接RAM的ADD0-ADD13,PCI映射空间的偏移地址为0-7FFEH,偶地址有效。LA15引入CPLD后可作为双口RAM的片选信号。

建立通讯的过程是PCI9054发送LHOLD信号,CPLD返回LHOLDA信号;PCI9054发出ADS信号,表示一次读写操作开始,此时CPLD锁存读写信号LW/R,并转换为RAM的R/W或OE信号;CPLD给PCI9054发送READY无效信号,使其保持等待状态。

信号握手的实现过程是:

PCI9054向RAM写数据→PCI9054通过USER0发出握手请求到CPLD→CPLD向DSP的IRQ发出中断信号→DSP响应中断→DSP读RAM数据。

评论