基于高速定点FFT算法的FPGA设计方案

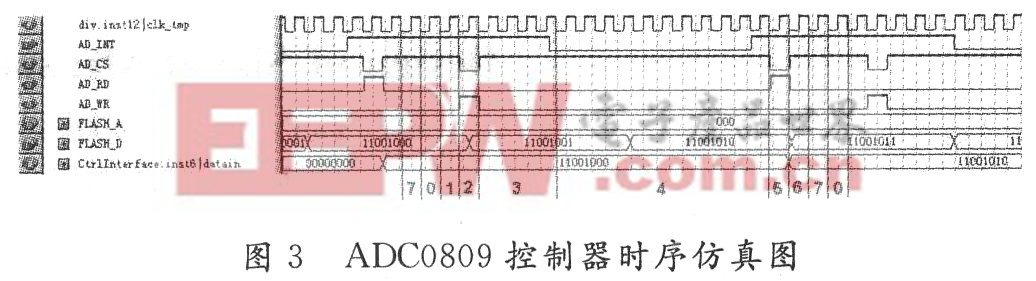

转接器有一定的工作规律。例如,当第0级变换做完进入转接器SW1前,先对后三路数据进行一定节拍的延时,延迟节拍分别为4,8,12。为了说明规律,把输入转接器的四路数据按照前后次序进行分组,每4个时钟节拍为1组,共16组,如图3(左)所示。在数据流串行经过转接器SW1时,第0组中的数据保持不变,第1组中的数据与第4组中的数据交换;5不变,2和8交换,3和12交换,6和9交换;10不变,7和13交换,11和14交换,15不变。交换完毕后,前三路数据经过延迟节拍分别为12,8,4的FIFO存储器输出,位置关系如图3所示。

上述转换规律对于SW2也是适用的,只是转接器前后的延时节拍和分组的大小有所不同。

2.2 存储单元

为了实现算法的流水线设计,存储器RAM设计为64×16 b的双端口RAM,即在时钟信号和写控制信号同时为低电平时,从输入总线写入RAM;在时钟信号和读控制信号同时为高电平时,从RAM输出数据。

ROM为17×16 b的ROM,储存经过量化后的旋转因子,旋转因子为正弦函数和余弦函数的组合。根据旋转因子的对称性和周期性,在利用ROM存储旋转因子时,可以只存储旋转因子的一部分。

2.3 运算结构

Radix-4蝶形运算单元是整个FFT处理器中的核心部件。在用Radix-4运算器计算时需要并行输入数据,如果能以并发数据输入的话,则同步性和控制度较好,但实际上常要进行串并之间的转换。存储RAM按单节拍输出16 b位宽数据,选择器不停旋转送入到确定的位置,每4点全部到位后R-4使能有效;然后4个时钟节拍得到有效结果数据,再通过选择器旋转送入到对应存储 RAM中。

复数运算中,对应复数的实部和虚部RAM用同一个地址发生器。地址发生器在进行RAM地址发生时采用两套地址,第一套是计数器按时钟节拍顺序产生的,用于输入数据的存储;第二套是由数据宽度为16 b的ROM产生的,ROM中存放的数据为下级运算所需倒序的序列地址,发生地址给RAM,然后RAM按倒序地址输出下级需要进行运算的数据。

2.4 块浮点结构

数字信号处理系统可分为定点制、浮点制和块浮点制,它们在实现时对系统资源的要求不同,工作速度也不同,有着不同的适用范围。定点制算法简单,速度快,但动态范围有限,需要用合适的溢出控制规则(如定比例法)适当压缩输入信号的动态范围。浮点表示法动态范围大,可避免溢出,但系统实现复杂,硬件需求量大,速度慢。

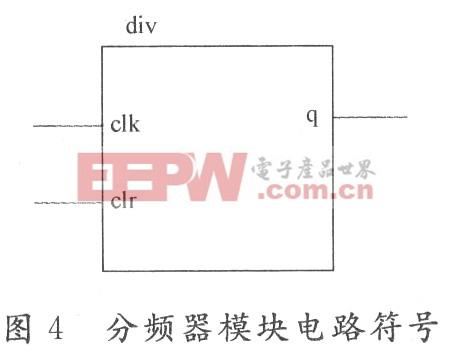

为了提高精度,并减少复杂度和存储量,采用块浮点结构。块浮点算法是以上两种表示法的结合。这种表示方法是,一组数共用同一个阶码,这个阶码是这组数中最大数的阶码。块浮点算法无需进行额外的指数运算,仅对尾数进行运算即可,其与定点运算一样方便,但需要在每级运算结束后进行本级运算溢出最大位数判断,以对数据块进行块指数调整。在调整时仅保留一位符号位,因而能够充分利用有限位长。这样处理比定点方法扩大了动态范围,并且提高了精度,比浮点运算在速度上有了提高。块浮点结构如图4所示。

3 结 语

着重讨论基于FPGA的64点高速FFT算法的实现方法。采用高基数结构和流水线结构,大大提高了FFT处理器的运行速度。同时块浮点结构的引入,也大幅减少了浮点操作占用FPGA器件的资源数目,兼顾了FPGA高精度、低资源、低功耗的特点。从实验结果看,该方法可以满足高速实时处理数字信号的要求。

评论