基于RocketIO接口的高速互连应用研究与实现

2.1 应用RapidIO协议买现板间互连

RapidIO是一种基于高性能包交换的开放式互连技术,主要功能是完成系统内部芯片到芯片和板到板之间的高速传输数据,能够提供高带宽、低时延、软件独立和高容错性的数据传输解决方案。同时支持点对点或点对多点的通信、DMA操作、消息传递模式交换数据以及多种拓扑结构等功能。

RapidIO采用3层分级体系结构,分别为物理层、传输层、逻辑层。物理层规范在整个分级结构的底部,包括器件级接口的细节,如包传输机制、流量控制、电气特性和低级错误管理。传输层规范在中间层,定义RapidIO地址空间和在端点器件间传输包所需的路由信息。逻辑层规范定义全部协议和包的格式,它们为端点器件发起和完成事物提供必要的信息。

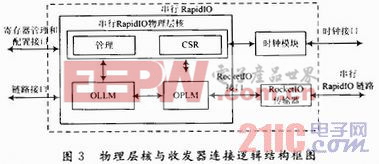

RapidIO串行物理层,通常称为串行RapidIO,是针对板上或通过背板的器件间的电气连接。串行物理层定义器件间的全双工串行链路,在每个方向上使用单向差分信号。RapidIO串行物理层实现链路训练、链路初始化,支持RapidIO器件间的包传送,包括包和控制符号的传送、流量控制、错误管理和其他器件到器件的功能。RapidIO物理层核与RocketIO收发器连接逻辑结构框图如图3所示。本文引用地址:http://www.eepw.com.cn/article/149180.htm

由于RapidIO逻辑层包被定义为一连串的比特,并且与物理层实现无关,所以RapidIO协议在串行与并行接口,铜线与光纤介质下都能正确工作。

其RapidIO串行物理层有如下特征:

(1)采用8 b/10 b编码方案将发送时钟嵌入到数据中。

(2)在每个方向上支持一个串行差分对或支持4个并列的串行差分对。

(3)使用专用的8 b/10 b码(称为K码)来管理链路,管理流量控制、包定界和错误报告。

(4)支持每通道1.25 Gb/s,2.5 Gb/s和3.125 Gb/s波特率(数据速率分别为1.0 Gb/s,2.0 Gb/s和2.5 Gb/s)的传送速率。

2.2 应用Fibre Channel协议实现系统间互连

光纤通道技术是综合计算机通道和数据网络概念提出的一个不同于传统的通道和网络结构的互连方案,采用通道技术控制信号传输,使用仲裁或交换方式处理共享冲突,并采用了基于信用的流量控制策略。

Fibre Channel模型分为5层,分别为:FC-0,FC-1,FC-2,FC-3和FC-4。FC-0层定义了连接的物理端口特性,包括介质和连接器、驱动器、接收机、发射机等的物理特性、电器特性和光特性、传输速率以及其他的一些连接端口特性。在本设计中,FC-0层处理由光电收发器实现光信号与电信号转换;FC-1层是信号编码和解码层,FC-1层处理由FPGA的RocketIO完成串并/并串转换、8 b/10 b编解码、有序集及位同步等;FC-1层使用8 b/10 b编码方式,这意味着每传输10 b数据,实际得到8 b的有效数据,其他两位是冗余位。信号可以被编码成2种字符集:K字符集(特殊的控制信号和命令)和D字符集(普通数据)。FC-2层是帧协议层,是FC用来识别、解释和处理FC网络信息流的核心层。FC-2层规定信息单元的组成格式、原语序列协议、端口类型、服务类型、数据的分段与重组、流量控制、差错恢复策略、节点初始化、节点的注册和节点的注销等功能。FC-0,FC-1和FC-2层这3层共同组成了FC物理层。FC-3层是FC的公共服务层,定义了如带宽频率分片、搜索组和多播等通用服务。FC-4:该层是FC协议模型的最高层,在本系统的设计中,使用了匿名签署消息传输协议(FC-AE-ASM)来满足系统中数据的传输需要。

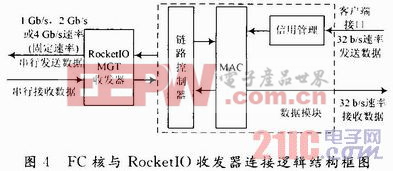

在FC核的嵌入式应用中。使用一个或2个RocketIO收发器来提供1 Gb/s,2 Gb/s或4 Gb/s的接口速率,利用FPGA中的8 b/10 b编解码器、CRC产生和校验单元以及接收弹性缓冲进行设计。FC核内部提供了32 b宽的Client接口,FC帧数据采用32 b/s访问。FC核的时钟在配置时已固定,分别可采用53.125 MHz和106.25 MHz。

FC核与RocketIO收发器连接逻辑结构框图如图4所示。

评论