基于ARM+FPGA的重构控制器设计

2.2 Tap状态机时序介绍

JTAG边界扫描测试由测试访问端口的TAP控制器管理。TMS,TRST和TCK引脚管理TAP控制器的操作,TDI和TDO位数据寄存器提供串行通道。TDI也为指令寄存器提供数据,然后为数据寄存器产生控制逻辑。对于选择寄存器、装载数据、检测和将结果移出的控制信号,由测试时钟 (TCK)和测试模式(TMS)选择两个信号控制。测试复位信号(TRST,一般以低电平有效)一般作为可选的第五个端口信号。

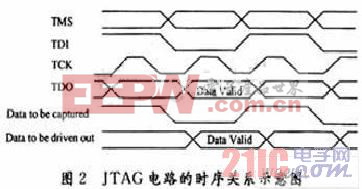

如图2所示,所有基于JTAG的操作都必须同步于JTAG时钟信号TCK。所有测试逻辑的变化(例如指令寄存器,数据寄存器等)必须出现在 TCK的上升沿或下降沿。关键时序关系是:TMS和TDI采样于TCK的上升边沿,一个新的TDO值将于TCK下降边沿后出现,因此一般情况下JTAG的时钟不会太高。

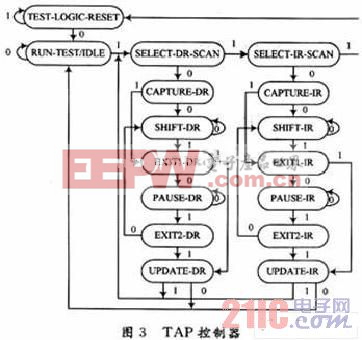

图3表示了IEEE 1149.1标准定义的TAP控制器的状态图,TAP控制器是16个状态的有限状态机,为JTAG接口提供控制逻辑。TAP状态转移如图3所示,箭头上的 1或0,表示TMS在TCK上升沿的值(高电平TMS=1,低电平TMS=0),同步时钟TCK上升沿时刻TMS的状态决定状态转移过程。对于TDI端输入到器件的配置数据有两个状态变化路径:一个用于移指令到指令寄存器中,另一个用于移数据到有效的数据寄存器,该寄存器的值由当前执行的JTAG指令决定。当TAP控制器处于指令寄存器移位(SHIFT-IR)状态时,对于每一个TCK的上升沿,连接在TDI和TDO之间的指令寄存器组中的移位寄存器向串行输出方向移一位。

当TMS保持为高电平时,在TCK的上升沿TAP控制器进入到“EXIT1-IR”状态;当TMS为低电平时,TAP控制器保持在“指令寄存器移位”状态。

评论