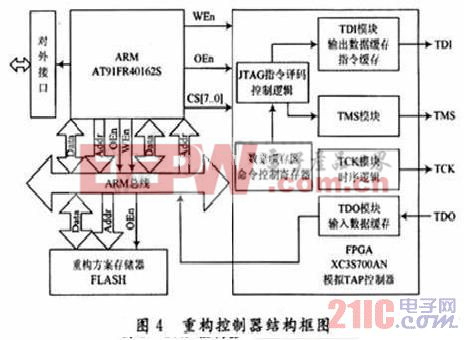

基于ARM+FPGA的重构控制器设计

3.1硬件系统组成

其主要功能是控制按照用户不同需求控制调用不同的方案配置目标可编程器件。它主要包括ARM处理器、FPGA、FLASH存储器和对外总线接口,各功能部件主要功能如下:

(1)ARM处理器选用AT91FR40162S,其主要功能是控制模拟JTAG接口的FPGA读取FLASH存储器中的重构方案,实现在系统配置;

(2)FPGA协处理器选用Xilinx公司SPARTEN3AN系列的XC3S700AN-FGG484,是基于非易失性存储的FPGA,自身带有PROM,它作为外部总线和ARM控制器之间的双端口,主要功能是模拟 JTAG接口实现TAP控制器时序,完成配置方案数据的并串转换并输出至外部总线;

(3)FLASH存储器容量为32M×16 b,用于处理器的上电引导、存放多种重构配置方案。由于要求的存储容量较大,采用SPANSION公司S29GL512P(32M×16 b)的存储空间,访问速度为110 ns,可以达到25 ns快速页存取和相应的90 ns随机存取时间,FBGA封装;

(4)外部总线接口,可采用1路RS 232驱动接收器,实现和外部通信的接口;

(5)测试线TCK,TMS,TDI和TDO,是重构控制器向目标可编程器件提供所需的JTAG TAP激励,分别控制目标多个FPGA的重构配置和反馈重构信息。

3.2重构控制器工作原理

ARM执行的初始化工作包括程序更新加载运行,FPGA参数设定等;FPGA设定内部寄存器和逻辑状态的初始值、内部缓冲区数据清零等。

重构控制器示意图如图4所示。图中ARM处理器一方面通过ARM总线读取外部FLASH中的配置方案,对其进行并串转化操作,将其存储到 FLASH存储器中;另一方面重构控制器中模拟TAP控制器的FPGA,从ARM内置的FLASH存储器中读取配置文件,并执行ARM处理器发出的指令解译该文件,重构控制器解释二进制文件方法如下:在ARM处理器的控制下,从装载配置文件的FLASH中读出一个字节,判断是哪条JTAG指令,然后根据指令的格式作具体的处理,产生TCK,TMS,TDI和TDO信号,作为目标可编程器件的JTAG接口激励,与目标可编程器件的JTAG口串联成菊花链,在 ARM处理器的控制下,对目标可编程器件进行在系统编程。被重构的FPGA由支持局部动态重构的Xilinx公司的Virtex-4系列FPGA来实现。

4 结 语

本文介绍的重构控制器既具有ARM微控制器所拥有的高速处理器核、体积小、集成度高、运算速度快、存储器容量大、功耗低等特点,又具有FPGA 强大的并行计算能力和方便灵活的动态可重构性,使硬件信息(可编程器件的配置信息)像软件程序一样被动态调用或修改。对于特定的目标FPGA芯片,在一定控制逻辑的驱动下,对芯片的全部或部分逻辑资源重新进行动态配置,从而实现硬件的时分复用,灵活快速地改变系统功能,节省逻辑资源,满足大规模应用需求。

评论