基于PSoC5 DMA的多路输入与ADC自动控制设计

摘要:本文介绍使用Cypress PSoC5中DMA实现多路输入切换以及ADC采样保存的自动控制,有效减少对CPU时间占用。

本文引用地址:https://www.eepw.com.cn/article/130721.htm概述

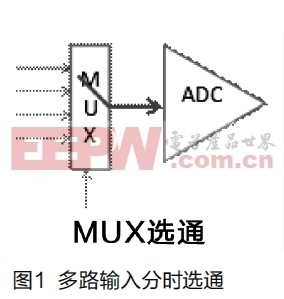

在系统设计中,很多时候会采用多路输入,分时切换选通进行ADC转换,可以减少ADC器件的数量。

图1是多路输入选通的结构图。目前很多芯片内部已经含有多路选择器,已经无需外接了。但是对于多路选通的控制,在一般的系统设计中都是需要采用软件代码写寄存器的方式实现。这种方法通常是在ADC转换完成触发中断,软件响应中断,再进行下一路输入的选通切换。所以,至少需要中断响应,压栈,寄存器读写,退栈,退出中断几个阶段。

在这种系统中,如果需要对多路输入做实时采样,CPU就需要频繁响应中断,主程序任务被频繁打断。显而易见,CPU时间额外开销会增加;在一些多任务系统中,还会因为需要有任务堆栈保存和切换[2],影响会更加明显。并且因为软件处理周期等原因,延长硬件切换和转换时间间隔,降低系统工作效率。

Cypress的PSoC5是基于ARM Cortex-M3内核的高性能芯片, 支持0.5~5.5V的宽范围电压输入。更重要的是,PSoC5内含非常丰富的可编程资源UDB(Universal Digital Blocks)[3],以及强大的DMA控制系统,可以非常方便地实现对各种外围资源的读取和控制。

通过PSoC5的DMA进行结构和配置都非常灵活[3],可以通过对UDB,SRAM,ADC等资源的操作,实现多路输入的全自动切换,而不需要CPU响应中断和软件干预,无需占用CPU的时间。

在PSoC5中的多路输入自动切换控制

评论