SuVolta发布Deeply Depleted Channel技术

致力于开发可微缩低功耗CMOS技术的公司SuVolta今日在2011年IEDM会议上发布其Deeply Depleted Channel (DDC - 深度耗尽通道)的技术细节。SuVolta的DDC技术是该公司的PowerShrink低功耗CMOS平台的组成部分。该低功耗技术已向业界证明可以在不影响速度的前提下降低功耗百分之五十。配合先进的电压降低手段,DDC技术甚至可以降低功耗达百分之八十或更多。

本文引用地址:http://www.eepw.com.cn/article/126723.htmSuVolta总裁兼首席执行官Bruce McWilliams博士称:“SuVolta的技术已经由实际芯片验证,在半导体工业界引起强烈反响。现在我们披露DDC晶体管技术细节,以便业界专家可以了解SuVolta的技术如何降低功耗,允许低电压运作,以及实现工艺微缩至20纳米以下。”

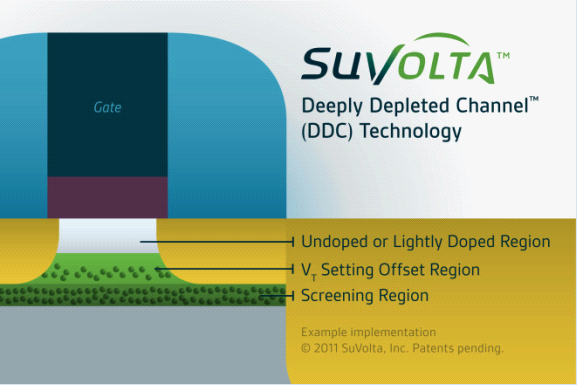

SuVolta Deeply Depleted Channel (DDC)晶体管技术

SuVolta的DDC晶体管降低阈值电压波动,以实现持续的CMOS微缩。该结构在门极加偏压时形成深度耗尽通道。在典型应用中,DDC通道包括几个部分:未掺杂或轻度掺杂区,VT设定区以及屏蔽区。不同应用中SuVolta的DDC晶体管会取决于芯片加工厂或特定芯片设计要求而略有不同。

未掺杂或轻度掺杂区去除通道中的杂质以形成深度耗尽通道。这将减小随机杂质波动(RDF)从而实现降低VDD,并提高载流子迁移率以增加有效电流。

VT设定区设定晶体管阈值电压而不影响载流子迁移率。该区也将改善传统晶体管的VT分布。

屏蔽区起屏蔽电荷并设定耗尽层深度的作用,并且其基体效应使得在需要的时候通过偏压动态调节VT成为可能。

DDC晶体管通过降低工作电压来实现低功耗运行。通过控制VT波动,使用SuVolta DDC技术设计的芯片将获益良多,包括:

· 工作电压降低百分之三十而不影响效能;

· 大幅降低漏电流;

· 减少设计“保护频带”;

· 提升良率。

此外,DDC晶体管允许设定多重VT,这对当今低功耗产品至关重要。除了显著降低VT波动所带来的优势,DDC晶体管还具备其他优点,可以在高速运作中进一步降低功耗。这些优点包括:

· 提高通道载流子迁移率从而增加驱动电流;

· 减小漏极引发势能降低(DIBL);

· 提高基体效应系数以实现更佳VT控制。

SuVolta公司首席技术长Scott Thompson博士指出:“有些时候单纯减小芯片尺寸并没有太大意义。光刻成本的增加导致每只晶体管成本饱和,正在终结摩尔定律。我相信目前的28nm和20nm将会是长期的技术结点。除了微处理器,移动市场的大多数芯片都更看重成本控制和低功耗。SuVolta的DDC结构独特之处在于它是唯一的可与现有CMOS工艺集成以及制造设备完全兼容的晶体管方案,使得半导体公司可以保持他们已有的电路知识产权。”

Kleiner Perkins Caufield & Byers合伙人Bill Joy表示:“工业界如果想持续发展移动电子产品,必须提升核心技术。SuVolta发明了基于平面基体CMOS工艺的突破性技术,用于解决半导体工业界最大的挑战 – 功耗”

评论