基于VW2010的视频存储系统的设计

引言

本文引用地址:https://www.eepw.com.cn/article/123969.htm常见的视频压缩技术有JPEG/2000、M-JPEG, MPEG1/2/4、H.263及H.264,其中MPEG4是基于第二代压缩编码技术制定的国际标准,具有高压缩比、可扩展性和可交互性等优点。对视频流压缩倍数可达450倍,分辨率输入可从320×240到1280×1024。与MPEG4和MPEG以往的版本相比,最大不同之处在于MPEG4使用“图层”(layer)方式,能够智能化选择影像的不同之处,在压缩编辑画面时,使图文件容量大幅缩减,从而加速音/视频的传输,适合于嵌入式视频存储系统体积小,存储容量适中的特性。

系统硬件设计

视频编解码芯片VW2010

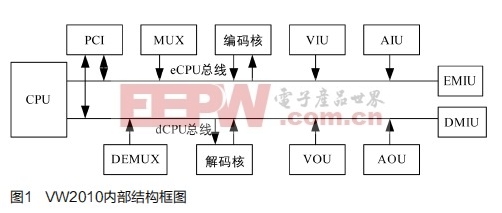

VW2010是VWEB公司开发的实时MPEG-4音视频压缩/解压芯片,可以把未经压缩的符合ITU-R.BT-656标准的视频信号,包括29.97帧/秒的NSTC制式和25帧/秒的PAL制式的电视信号压缩为MPEG-1/2/4或H.263格式,把I2C的音频信号压缩为MPEG-1、MP3、AAC或AC3格式。VW2010芯片结构如图1所示,图中给出了芯片的内部视频处理模块以及外部接口模块。

VW2010的编码部分有视频输入和音频输入两个输入模块,一个输出模块MUX,压缩数据输出CDO端口和Hot/PCI端口。内部的视频编码视频输入单元(VIU)将视频信号读入,利用水平方向的8通道滤波器和垂直方向的4信道滤波器将视频信号进行缩放,把视频图像调整为从sub-QCIF到全Dl的格式,并可以对图像进行亮度色度变换、视频输入解码和提取时间信息等操作。VW2010的解码部分有两个输入模块:DEMUX和HIU;两个输出模块:视频输出单元(VOU)和音频输出单元(AOU);两个输入端口:CDI和Host/PCI,系统host可直接通过主机接口对VW2010进行控制,MPEG数据流采用DMA方式传输。

基于VW2010的视频压缩系统硬件设计

本系统集成一片VW2010芯片对一路音视频流进行编解码,FPGA采用Altera公司的EP3C16Q240C8N, 用来设计各种接口连接各芯片,DSP采用TI的TMS320C2812,用来存储和加载各芯片初始化程序和配置信息。具体的系统硬件框图如图2所示。

评论