莱迪思半导体发布适用于HDMI、DVI和7:1 LVDS的视频显示接口套件

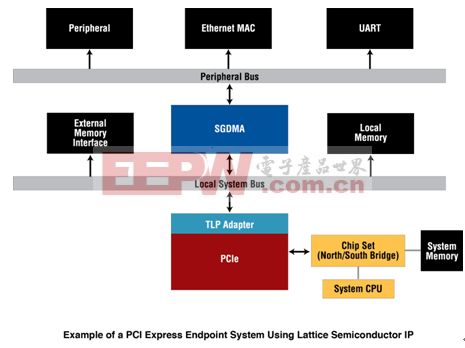

莱迪思半导体公司今日发布了即可获取的全面的视频显示接口套件,适用于高清多媒体接口(HDMI 1.3a)、数字视频接口(DVI)和7:1 LVDS接口。所有这些显示接口都可以作为获奖的中档LatticeECP3™的参考设计免费获得,一些免费的参考设计还可以移植到LatticeECP2M™和LatticeXP2™ FPGA系列。经芯片验证的参考设计使嵌入式、数字显示牌和工业客户能够设计高性能的娱乐、信息和视频系统。基于FPGA的可编程解决方案还可以使客户快速实现其专有的图像处理功能,这将有助于其产品的差异化。

本文引用地址:https://www.eepw.com.cn/article/113132.htm莱迪思针对整个显示应用细分市场,为三种主流多媒体标准提供了全面的解决方案。HDMI解决方案适用于处理从网络服务器、工业摄像机以及其他信号来源,到放映机和其他视频显示器的高清、非复制保护的音频-视频信号。DVI解决方案专门针对数字显示牌、消费和工业客户,其应用仅需要视频而不需要音频,并且他们对任何额外的使用权费用比较敏感。7:1 LVDS解决方案十分适合于在电子系统(嵌入式应用)中的板和板之间,传输大量视频数据。

经芯片验证的参考设计为三种主流的视频标准实现了物理层功能,以实现可靠、有效的串行传输。第一个参考设计,HDMI物理接口,充分利用了LatticeECP3 SERDES和其相关的PLL来自动检测HDMI的分辨率。这使得用户不需要编写处理器固件,从而使设计能够使用更少的元件,并且获得更快的产品上市时间。通过去除了分立的PHY并且集成到LatticeECP3器件中,进一步节约了成本。

第二个参考设计,DVI物理接口,采用最小变换差分信号(Transition Minimized Differential Signaling)机制,编码/解码和串行/解串LatticeECP3 FPGA中低功耗嵌入式SERDES上的视频数据。它可以发送和接收DVI视频数据。

第三个参考设计,在具有1Gbps LVDS功能的源同步差分I/O上实现了7:1 LVDS物理接口。此参考设计利用了较新的莱迪思FPGA系列中独特的工程预制I/O元件,如:高速LVDS缓冲器、DDR寄存器、精确PLL和内置的gearbox逻辑,以实现数据速率的最优化管理。嵌入式应用还经常需要在传输之前或之后进行图像和视频处理。莱迪思的低成本、中档FPGA使得设计师们能够构建集成的器件,同时拥有数据处理和有效的数据传输功能。

“我们很高兴能为我们的客户提供开发先进、高性能的视频显示应用的全面的视频显示接口套件”,莱迪思半导体公司的高密度解决方案市场部总监,Shakeel Peera说道,“莱迪思致力于提供全面的芯片开发资源支持,包括评估套件、参考设计、软件工具和IP核,帮助我们的客户加快其产品上市时间。”

欲了解更多有关莱迪思半导体提供的视频显示解决方案的信息,请访问http://www.latticesemi.com/video。免费的参考设计和相关文档还可以从莱迪思网站下载。

评论