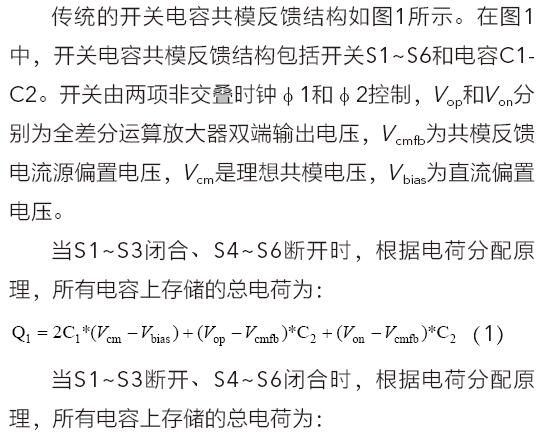

- 提出并设计了一种应用于CMOS全差分运放结构中的共模反馈电路。同传统结构的共模反馈结构相比,该结构能够使输出共模电平具有零延迟建立的特性,同时,不影响全差分运算放大器的输出摆幅,并且相较于传统结构,减少了开关数量,降低了开关电荷注入、时钟馈通,消除了初始电荷的影响。此新型共模反馈结构既有连续时间共模反馈速度较快、精度较高的优点,又有开关电容共模反馈输出摆幅大线性度好的优点。基于 Cadence spectre 对电路进行了仿真验证,结果表明,该结构的共模反馈具有快速的建立时间以及较大的输出摆幅。

- 关键字:

全差分运算放大器 共模反馈 输出摆幅 建立时间 201808

- 数字电路中的几个基本概念-建立时间(setuptime)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器...

- 关键字:

数字电路 建立时间 保持时间

- 对于大多数 ADC 用户来说,“时延”和“建立时间”这两个术语有时可以互换。但对于ADC 设计人员而言,他们非常清楚这两个术语的区别,以及这些现象将会如何影响您的应用电路。ADC 用户已注意到这两个 ADC 特性会对他们的电路产生一些影响,这是一个不争的事实,但是,人们对于时延和建立时间普遍存在误解,因此当一个系统设计人员绞尽脑汁地想要找出信号完整性问题的时候,可能受挫。

无论转换器采用一

- 关键字:

ADC 时延 建立时间 模拟IC

建立时间介绍

您好,目前还没有人创建词条建立时间!

欢迎您创建该词条,阐述对建立时间的理解,并与今后在此搜索建立时间的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473