- FPGA verilog实现的1602时钟计数器-网上很少用人公开这一类代码,一搜FPGA 1602,都是写一个静态的显示,在实际应用中,是没有用的,因此这个简单的例子,给大家抛砖引玉了!

- 关键字:

FPGA 1602时钟计数器

- 如何使用PlanAhead/Adept加速管脚排布-在排布FPGA管脚生成ucf文件的过程中,当FPGA管脚较多的时候,手工排布管脚不仅效率低,而且很容易出错。借助PlanAhead和Adept等工具,可以很方便快速的实现管脚排布。

- 关键字:

PlanAhead Adept FPGA

- 组合逻辑设计中的毛刺现象-和所有的数字电路一样,毛刺也是FPGA电路中的棘手问题,它的出现会影响电路工作的稳定性,可靠性,严重时会导致整个数字系统的误动作和逻辑紊乱。

- 关键字:

毛刺 FPGA 电路

- FPGA管脚分配时需注意的一些事项-设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚,不能用N类型管脚等等。

- 关键字:

FPGA

- 学习FPGA需要注意的几个重要问题-如何学好FPGA呢,很多人很困惑,多数停留在基础位置徘徊,我就这方面问题给大家谈几点自己的看法。

- 关键字:

FPGA 数字电路 HDL语言

- FPGA专家教您如何在FPGA设计中使用HLS-Luke Miller并非一开始就是HLS(高层次综合)的倡导者。在使用早期的工具版本的时候,他似乎有过一些糟糕的经历。

- 关键字:

FPGA HLS

- 参考时钟对SERDES性能的影响-我们知道,SERDES对参考时钟有严格的相位噪声性能要求。通常,SERDES供应商会根据其SERDES采用的PLL以及CDR架构特点,以及性能数据,提出对参考时钟的相位噪声的具体要求。

- 关键字:

SERDES 参考时钟 XILINX

- 深度学习算法有望在FPGA和超级计算机上运行-由NSF资助的一个研究项目,目前正在研究如何使用RDMA高性能连接器将深度学习算法在FPGA和跨系统之间运行;另一个由Andrew Ng和两个超算专家牵头的项目,则希望把模型放在超级计算机上,给它们一个Python接口。

- 关键字:

FPGA 深度学习 人工智能

- 不可错过的400Gbps以太网演示-在那里,毫无疑问你会驻足在赛灵思展位前(# 23)观看一个基于赛灵思Virtex UltraScale VU095 FPGA评估板VCU109的Spirent 400G以太网测试系统,该系统连接四个100Gbps的住友电工 CFP4 LR4光模块。

- 关键字:

赛灵思 FPGA 光模块

- 一个FPGA中现在可集成多少32位RISC处理器?-Jan Gray是在FPGA中集成32位RISC处理器的专家,他写了一篇博客叫作FPGA CPU 新闻,副标题为 “使用FPGA开发并行计算机体系架构”。

- 关键字:

FPGA RISC处理器

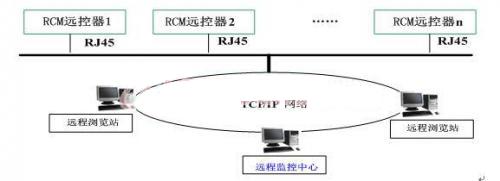

- 基于FPGA开放流程的SDN转发引擎-博主Greg Ferro在其Ethereal Mind网页上发布了一则关于 Corsa Technology简短博客信息,提到Corsa公司制作了一对基于FPGA开放流程的SDN转发引擎。Ferro同时简单讨论了此引擎是否适用于WANs网络。

- 关键字:

SDN FPGA WAN

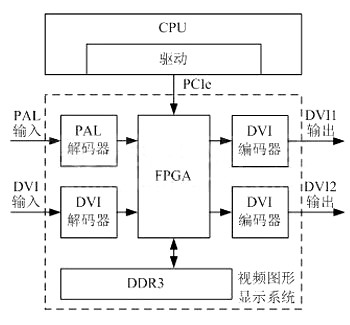

- 嵌入式视觉系统的构建模块-在本文中我们将会介绍嵌入式视觉系统的高级元素;如何简便快捷地使用软件 API 和 IP 库构建嵌入式视觉系统,如何把算法开发的增值部分添加到图像处理链中。

- 关键字:

FPGA 嵌入式

- 片内时钟的组合思路和设计技巧-我们都知道,当奇数个反相器串联在一起,并且把最后一级的输出反馈给第一级的输入时,在逻辑上会产生震荡,这样的电路结构通常被称为Ring OSC。

- 关键字:

FPGA RingOSC 片内时钟

- 详细解读Zynq的三种启动方式(JTAG,SD,QSPI)-本文介绍zynq上三种方式启动文件的生成和注意事项,包括只用片上RAM(OCM)和使用DDR3两种情况。 JTAG方式 JTAG方式是调试中最常用的方式,在SDK中 在“Project Explorer”窗口工程上右键->Debug As->Debug Configurations可以看到以下窗口 首次打开左边窗口中Xilinx C/C++ application(GDB)下没有子项,这时双击Xilinx C/C++ application(GD

- 关键字:

Xilinx RAM

xilinx fpga介绍

Xilinx FPGA

Xilinx FPGA主要分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如Spartan系列;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,如Virtex系列,用户可以根据自己实际应用要求进行选择。 在性能可以满足的情况下,优先选择低成本器件。

Xilinx FPGA可编程逻辑解决方案缩短了电子设备制造商开发产品的时间 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473