vhdl.programming 文章 最新资讯

基于SystemC的系统级芯片设计方法研究

- 随着集成电路制造技术的迅速发展,SOC设计已经成为当今集成电路设计的发展方向。SO C设计的复杂性对集成电路设计的各个层次,特别是对系统级芯片设计层次,带来了新挑战,原有的HDL难以满足新的设计要求。 硬件设计领域有2种主要的设计语言:VHDL和Verilog HDL。而两种语言的标准不统一,导致软硬件设计工程师之间工作交流出现障碍,工作效率较低。因此,集成电路设计界一直在寻找一种能同时实现较高层次的软件和硬件描述的系统级设计语言。Synopsys公司与Coware公司针对各方对系统级设计语言的

- 关键字: SOC SystemC 集成电路 VHDL Verilog HDL

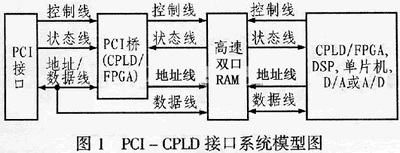

简易通用型PCI接口的VHDL-CPLD设计

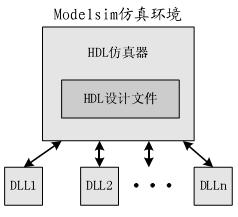

- 用CPLD设计所构成的CPI接口系统具有简洁、可靠等优点,是一种行之有效的设计途径。很多技术杂志和网站上,都有不少用CPLD设计PCI常规传输系统的文章。但用这些方法在MzxPlusII、Fundition等环境下进行模拟仿真时,其产生的时序往往与PCI规范有很大出入。虽然 Altera 等公司推出PCI核可以直接使用,但这样的内核占用CPLD资源较多,且能适配的器件种类少,同时价格也高,在实际设计应用中有很大的局限性。因此,使用通用型CPLD器件设计简易型PCI接口有很大的现实意义。在Compact

- 关键字: VHDL-CPLD

AC-Link数字音频VHDL编/解码的FPGA设计

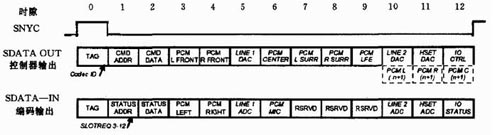

- 引言 数字音频处理是指为真实再现声音的逼真效果而对音频进行的编解码处理技术,它是宽带网络多媒体、移动多媒体通信的关键技术.Audio Codec′97(音频数字信号编/解码器)是其中一种用于声音录放的技术标准,简称AC′97. AC′97采用双集成结构,即Digital Controller(数字信号控制器)和Audio Codec(音频编解码),使模/数转换器ADC和数?模转换器DAC转换模块独立,尽可能降低EMI(电磁干扰)的影响。 利用FPGA,可

- 关键字: FPGA VHDL

AC-Link数字音频VHDL编/解码的FPGA设计

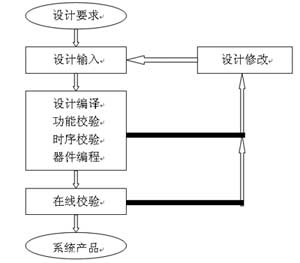

- 提出一种利用FPGA实现AC-Link数字音频处理的设计方案.AC-Link音频编解码系统以VHDL模块进行设计,经过波形仿真和结果验证后,将程序下载到FPGA中实现1这种设计方法可以缩短设计周期,提高设计的可靠性和效率。 引言 数字音频处理是指为真

- 关键字: AC-Link VHDL FPGA

基于现场可编程门阵列的数控延时器的设计

- l 引言 利用硬件描述语言结合可编程逻辑器件(PLD)可以极大地方便数字集成电路的设计,本文介绍一种利用VHDL硬件描述语言结合现场可编程门阵列(FPGA)设计的数控延时器,延时器在时钟clk的作用下,从8位数据线输入延时量,到LATCH高电平时锁存数据,可以实现对触发脉冲TRIG的任意量的延时。由于延时范围不同,设计所用到的FPGA的资源也不同,本文详细介绍最大延时量小于触发脉冲周期的情况。该延时器的软件编程和调试均在MuxplusⅡ环境下完成,系统设计选用Altera公司的EPFl0K30A

- 关键字: VHDL 现场可编程门阵列

一种用VHDL设计实现的有线电视机顶盒信源发生方案

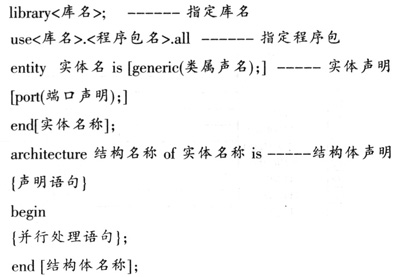

- VHDL是随着可编辑逻辑器件(PLD)的发展而发展起来的一种硬件描述语言。它是1980年美国国防部VHSIC(超高速集成电路)计划的一部分,并于1986年和1987年分别成为美国国防部和IEEE的工业标准。作为一种硬件设计时采用的标准语言,VHDL具有极强的描述能力,能支持系统行为级、寄存器传输级和门级三个不同层次的设计,这样设计师将在TOP-DOWN设计的全过程中均可方便地使用同一种语言。而且,VHDL设计是一种“概念驱动式”的高层设计技术,设计人员毋需通过门级原理图描述电路

- 关键字: VHDL

使用VHDL语言设计FPGA的几个常见问题的探讨

- 详细讨论了在MAX plusⅡ开发平台下使用VHDL硬件描述语言设计现场可编程门阵列(FP-GA)时常见的三个问题:等占空比分频电路、延时任意量的延时电路、双向电路。 1 引言 随着EDA技术的发展,使用硬件语言设计可编程逻辑器件(PLD)/现场可编程门阵

- 关键字: VHDL FPGA 问题

vhdl.programming介绍

您好,目前还没有人创建词条vhdl.programming!

欢迎您创建该词条,阐述对vhdl.programming的理解,并与今后在此搜索vhdl.programming的朋友们分享。 创建词条

欢迎您创建该词条,阐述对vhdl.programming的理解,并与今后在此搜索vhdl.programming的朋友们分享。 创建词条