- 本设计采用可编程芯片和VHDL语言进行软硬件设计,不但可使硬件大为简化,而且稳定性也有明显提高。由于可编程芯片的频率精度可达到50 MHz,因而计时精度很高。本设计采用逐位设定预置时间,其最长时间设定可长达99小

- 关键字:

240C Q240 VHDL 240

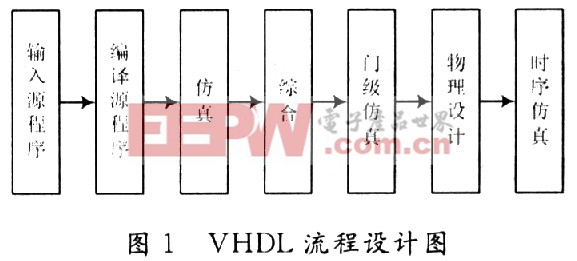

- 应用VHDL语言设计数字系统,大部分设计工作可在计算机上完成,从而缩短系统开发时间,提高工作效率。下面介绍...

- 关键字:

VHDL 交通灯控制器

- CPLD设计的CCD信号发生器技术,本文设计了一种基于CPLD的可编程高精度CCD信号发生器。充分利用CPLD的可编程性.模拟出满足系统要求的CD信号,输出信号频率达到1IMHZ。1 引言

CCD (Charge Coupled Devices)电荷藕合器件是20世纪70年代初发展起来

- 关键字:

技术 信号发生器 CCD 设计 CPLD

- IP(IntellectualPropcrty)就是常说的知识产权。美国Dataquest咨询公司将半导体产业的IP定义为用于ASIC...

- 关键字:

IP核 晶闸管 EDA VHDL

- VHDL设计的串口通信程序,本模块的功能是验证实现和PC机进行基本的串口通信的功能。需要在

PC机上安装一个串口调试工具来验证程序的功能。

程序实现了一个收发一帧10个bit(即无奇偶校验位)的串口控

制器,10个bit是1位起始位,8个数据位

- 关键字:

程序 通信 串口 设计 VHDL

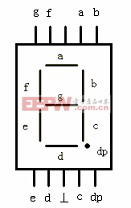

- CPLD设计的驱动数码显示电路案例,显示原理:

八段数码显示管如图1.1 所示,八段数码管每一段为一发光二极管,共有a~g 以及小数点dp 八个发光二极管。将八段数码管中的每个二极管的阴极并联在一起,组成公共阴极端。这样把共阴极管脚接地,此时

- 关键字:

电路 案例 显示 数码 设计 驱动 CPLD

- 传统的定时器硬件连接比较复杂,可靠性差,而且计时时间短,难以满足需要。本设计采用可编程芯片和VHDL语言进行软硬件设计,不但可使硬件大为简化,而且稳定性也有明显提高。由于可编程芯片的频率精度可达到50 MHz,因而计时精度很高。本设计采用逐位设定预置时间,其最长时间设定可长达99小时59分59秒。完全可以满足用户的需要,使用也更为方便。

- 关键字:

VHDL 定时器

- CPLD(ComplexprogrammableLogicDevice,复杂可编程逻辑器件)是在传统的PAL、GAL基础上发展而来的,具有...

- 关键字:

CPLD DSP 人机接口模块

- 在此将VHDL语言设计的计数器应用于脉搏测量,精确的计量出脉搏跳动,并通过数码管直观地表示出来。显示出VHDL语言设计数字系统与医学的紧密联系及其在医疗实践中的巨大应用前景。实践证明,将EDA技术与医学相结合,不仅能促进EDA技术的深入发展,而且能够极大地推动医学的进步。

- 关键字:

医学 应用 技术 EDA 语言 核心 VHDL

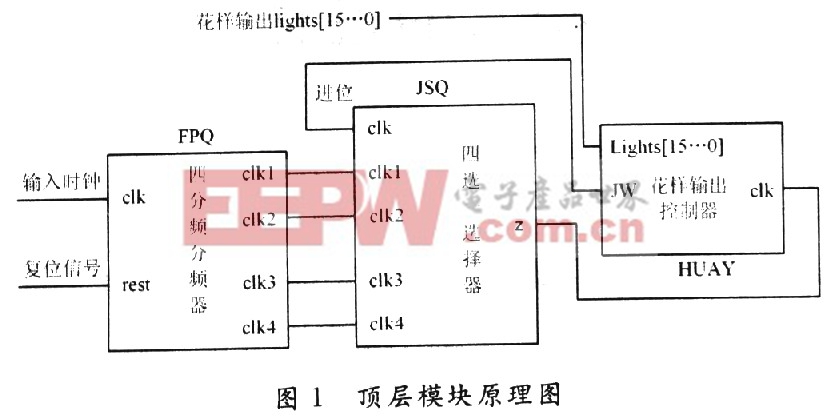

- 介绍一种基于VHDL的可变速彩灯控制器的设计方案,该系统无需外加输入信号,只需一个时钟信号就能实现以4种不同速度循环演示8种花型。该系统较以前的传统设计具有硬件电路简单、体积小、功耗低、可靠性高等特点。特别是可以在不修改硬件电路的基础上,仅通过更改软件就能实现任意修改花型的编程控制方案,而且设计非常方便,设计的电路保密性强。

- 关键字:

控制器 设计 彩灯 变速 VHDL 基于

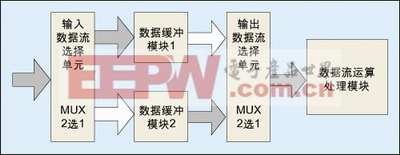

- 常用FPGA/CPLD四种设计技巧,FPGA/CPLD的设计思想与技巧是一个非常大的话题,本文仅介绍一些常用的设计思想与技巧,包括乒乓球操作、串并转换、流水线操作和数据接口的同步方法。希望本文能引起工程师们的注意,如果能有意识地利用这些原则指导日

- 关键字:

技巧 设计 FPGA/CPLD 常用

vhdl-cpld介绍

您好,目前还没有人创建词条vhdl-cpld!

欢迎您创建该词条,阐述对vhdl-cpld的理解,并与今后在此搜索vhdl-cpld的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473