- 一、多路彩灯控制器设计原理设计一个彩灯控制程序器。可以实现四种花型循环变化,有复位开关。整个系统共有三个输入信号CLK,RST,SelMode,八个输出信号控制八个彩灯。时钟信号CLK脉冲由系统的晶振产生。各种不同花

- 关键字:

VHDL 多路 灯控 制器设计

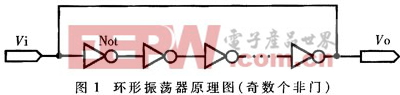

- 采用CPLD的片内环形振荡器的方案设计,本文介绍一种通用的基于CPLD的片内振荡器设计方法,它基于环形振荡器原理,只占用片上普通逻辑资源(LE),无需使用专用逻辑资源(如MaxII中的UFM),从而提高了芯片的资源利用率;振荡频率可在一定范围内调整,振荡输出

- 关键字:

方案设计 振荡器 内环 CPLD 采用

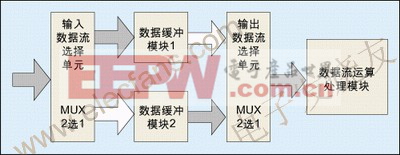

- FPGA/CPLD设计思想与技巧简介,本文讨论的四种常用FPGA/CPLD设计思想与技巧:乒乓操作、串并转换、流水线操作、数据接口同步化,都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作中取得事半功倍的效果。 F

- 关键字:

简介 技巧 设计思想 FPGA/CPLD

- 随着科技的飞速发展、高分辨率的数模混合电路的应用不断深入,电路设计日趋复杂,精度越来越高,所以高精度AD转换电路的设计就成了仪器仪表及各种测量控制系统的难点。本系统来源于仪器仪表的温控系统设计,采用高精

- 关键字:

CPLD VFC AD转换器

- 1 引 言EDA是现代电子系统设计的关键技术。硬件描述语言VHDL以其“代码复用”(code re-use)远高于传统的原理图输入法等诸多优点,逐渐成为EDA技术中主要的输入工具。然而,基于IEEE VHDL Std 1076-1993标准

- 关键字:

VHDL-AMS 控制系统 分析 中的应用

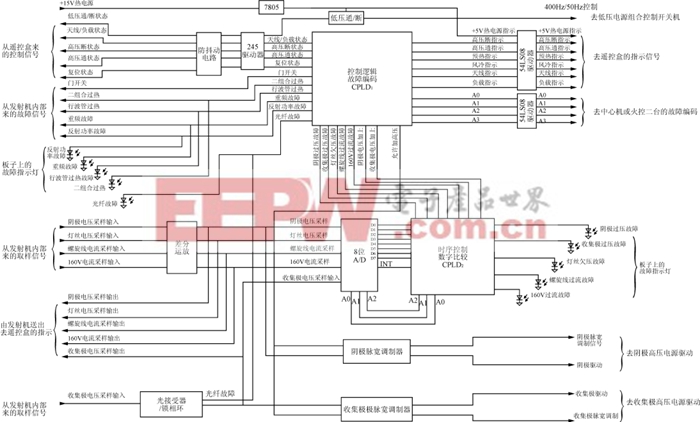

- 摘要:可编程控制器(PLD)自20世纪60年代末出现以来,就以其灵活、高效、可靠性高等优点受到设计者的青睐。而CPLD是20世纪90年代推出的一种复杂的PLD,其主要特征是集成规模大于1000门以上的可编程逻辑器件。它以其

- 关键字:

系统 介绍 保护 控制 CPLD 发射机 基于

- 1 引言随着社会的发展。使用电梯越来越普遍,已从原来只在商业大厦、宾馆过渡到在办公室、居民楼等多种建筑中,并且对电梯功能的要求也不断提高,其相应控制方式也在不断发生变化。电梯的微机化控制主要有:PLC控制、

- 关键字:

CPLD VDHL 器件 电梯控制系统

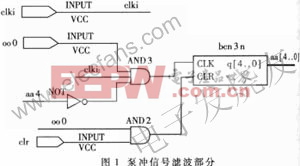

- 基于CPLD的数字滤波及抗干扰实现,1 滤波和抗干扰概述

单片机应用系统的输入信号常含有种种噪声和干扰,它们来自被测信号源、传感器、外界干扰源等。为了提高测量和控制精度,必须消除信号中的噪声和干扰。噪声有两大类:一类为周期性的;另一类为

- 关键字:

抗干扰 实现 波及 数字 CPLD 基于

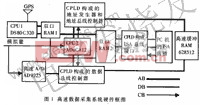

- 基于CPLD和MAX7000系列的数据采集系统简介,CPLD是复杂的PLD,专指那些集成规模大于1000门以上的可编程逻辑器件。它由与阵列、或阵列、输入缓冲电路、输出宏单元组成,具有门电路集成度高、可配置为多种输入输出形式、多时钟驱动、内含ROM或FLASH(部分支持在系

- 关键字:

系统 简介 数据采集 系列 CPLD MAX7000 基于

- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

DSP FPGA CPLD

- 摘 要:本控制仪以单片机80c196kc为核心,集无功补偿、电度量计量、电能质量监测及通信于一体,能实时显示电网的各项参数,通过键盘可人工设定系统运行的参数。单片机外围芯片PSD8XX及复杂可编程逻辑器件(CPLD)的使

- 关键字:

CPLD 无功补偿 控制仪 键盘设计

- EDA技术是以计算机为工具完成数字系统的逻辑综合、布局布线和设计仿真等工作。电路设计者只需要完成对系统功能的描述,就可以由计算机软件进行系统处理,最后得到设计结果,并且修改设计方案如同修改软件一样方便。利用

- 关键字:

VHDL FPGA 自动售货机 控制模块

- 一、硬件电路设计本文选用CPLD 是ALTERA 公司的EPM240T100,结合MAX232 接口芯片进行串口通信设计,框图如下图1 所示。

图1 CPLD串口通信模块硬件设计二、VHDL程序模块设计及描述使用VHDL 对CPLD 进行编程,设计3 个

- 关键字:

CPLD 串口 电路设计

- 可编程逻辑器件(PLD,Programmable Logic Device)的灵活性一直受到电子工程师的喜爱,但在各种移动式消费类电子产品市场仍然是ASIC芯片的天地。有几个原因阻碍着CPLD器件进入移动设备市场,尤其是各种基于电池供电的

- 关键字:

CPLD 便携式应用 零功耗 系统

- 本设计采用可编程芯片和VHDL语言进行软硬件设计,不但可使硬件大为简化,而且稳定性也有明显提高。由于可编程芯片的频率精度可达到50 MHz,因而计时精度很高。本设计采用逐位设定预置时间,其最长时间设定可长达99小

- 关键字:

240C Q240 VHDL 240

vhdl-cpld介绍

您好,目前还没有人创建词条vhdl-cpld!

欢迎您创建该词条,阐述对vhdl-cpld的理解,并与今后在此搜索vhdl-cpld的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473