- 电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

- 关键字:

VHDL 发接复用器 DH系统 FPGA仿真

- 基于VHDL和发接复用器的SDH系统设计及FPGA仿真, 针对目前国内SDH系统中还没有一个专门的E1分接复用芯征,本文介绍一种用高级硬件描述语言VHDL及状态转移图完成该发接复用器的设计的新型设计方法及其FPGA实现。并给出了用Xilinx FoundaTIon tools EDA软件设计的

- 关键字:

设计 FPGA 仿真 系统 SDH VHDL 复用器 基于

- 基于FPGA和VHDL语言的多按键状态识别系统, 这里提出一种利用FPGA的I/0端口数多和可编程的特点,采用VHDL语言的多按键状态识别系统,实现识别60个按键自由操作,并简化MCU的控制信号。 2 系统设计方案 FPGA是一种可编程逻辑器件,它具有良好性能、极高

- 关键字:

状态 识别 系统 按键 语言 FPGA VHDL 基于

- 摘要:介绍了SDH系统中的接口电路――数字分接复用器的VHDL设计及FPGA实现。该分接复用器电路用纯数字同步方式实现,可完成SDH系统接口电路中7路(可扩展为N路)E1数据流的分接和复用。该设计显示了用高级硬件描述语

- 关键字:

FPGA VHDL SDH 接口

- VHDL是随着可编辑逻辑器件(PLD)的发展而发展起来的一种硬件描述语言。它是1980年美国国防部VHSIC(超高速集...

- 关键字:

PLD VHDL 机顶盒 信源

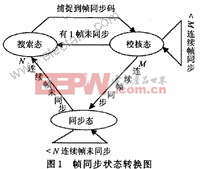

- 数字通信网中,帧同步是同步复接设备中最重要的部分,他包括帧同步码的产生和帧同步码的识别,其中接收端的帧同步识别电路的结构对同步性能的影响是主要的。

1 工作原理

实现帧同步的基本方法是在发送端预先规

- 关键字:

算法 同步 实现 语言 VHDL

- 在通信系统中,由于信道存在大量的噪声和干扰,使得经信道传输后的接收码与发送码之间存在差异,出现误码。在...

- 关键字:

VHDL 编译码器 线性分组码

- 数字信号在传输过程中受到干扰的影响,降低了其传输的可靠性,线性分组码作为一种常用的信道编码,在通信传输系统中应用广泛。在对线性分组码的编译码规则研究基础上,讨论了生成矩阵、监督矩阵与错误图样集之间的关系,在Max+PlusⅡ开发环境中,用VHDL语言设计线性分组码编译码器,对其各项设计功能进行了仿真和验证。结果表明,该设计正确,其功能符合线性分组码编译码器的要求。

- 关键字:

VHDL 线性 分组码 编译码器

- 本设计采用可编程芯片和VHDL语言进行软硬件设计,不但可使硬件大为简化,而且稳定性也有明显提高。由于可编程芯片的频率精度可达到50 MHz,因而计时精度很高。本设计采用逐位设定预置时间,其最长时间设定可长达99小

- 关键字:

240C Q240 VHDL 240

- 应用VHDL语言设计数字系统,大部分设计工作可在计算机上完成,从而缩短系统开发时间,提高工作效率。下面介绍...

- 关键字:

VHDL 交通灯控制器

- IP(IntellectualPropcrty)就是常说的知识产权。美国Dataquest咨询公司将半导体产业的IP定义为用于ASIC...

- 关键字:

IP核 晶闸管 EDA VHDL

- VHDL设计的串口通信程序,本模块的功能是验证实现和PC机进行基本的串口通信的功能。需要在

PC机上安装一个串口调试工具来验证程序的功能。

程序实现了一个收发一帧10个bit(即无奇偶校验位)的串口控

制器,10个bit是1位起始位,8个数据位

- 关键字:

程序 通信 串口 设计 VHDL

vhdl-ams介绍

即IEEE 1076.1标准。

VHDL-AMS是VHDL的一个分支,它支持模拟、数字、数模混合电路系统的建模与仿真。

http://www.eda.org/vhdl-ams/

Verilog-AMS与之类似。支持模拟、数字、数模混合电路系统的建模与仿真。

http://www.eda.org/verilog-ams/

The VHDL-AMS language [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473