lattice 文章 最新资讯

Lattice MXO2: 计时控制

- Warning: file_get_contents(https://www.eetree.cn/wiki/_media/%E8%AE%A1%E6%97%B6%E5%99%A8%E6%A1%86%E5%9B%BE.png?w=800&tok=0acdce): failed to open stream: HTTP request failed! HTTP/1.1 403 Forbidden in /var/www/html/www.edw.com.cn/www/rootapp/controll

- 关键字: 计时器 FPGA Lattice Diamond 小脚丫

Altera MAX10: 按键消抖

- 按键消抖在之前的实验中我们学习了如何用按键作为FPGA的输入控制,在本实验中将学习如何进行按键消抖,用按键完成更多的功能。====硬件说明====按键是一种常用的电子开关,电子设计中不可缺少的输入设备。当按下时使开关导通,松开时则开关断开,内部结构是靠金属弹片来实现通断。按键抖动的原理抖动的产生 :通常的按键所用的开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,为了不产生这种现

- 关键字: 消抖 FPGA Lattice Diamond 小脚丫

Lattice MXO2: 按键消抖

- 按键消抖在之前的实验中我们学习了如何用按键作为FPGA的输入控制,在本实验中将学习如何进行按键消抖,用按键完成更多的功能。硬件说明按键是一种常用的电子开关,电子设计中不可缺少的输入设备。当按下时使开关导通,松开时则开关断开,内部结构是靠金属弹片来实现通断。按键抖动的原理抖动的产生 :通常的按键所用的开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,为了不产生这种现象而作的措施就是

- 关键字: 消抖 FPGA Lattice Diamond 小脚丫

Altera MAX10: LED流水灯

- 在时钟分频实验中我们练习了如何处理时钟,接下来我们要学习如何利用时钟来完成时序逻辑。====硬件说明====流水灯实现是很常见的一个实验,虽然逻辑比较简单,但是里面也包含了实现时序逻辑的基本思想。要用FPGA实现流水灯有很多种方法,在这里我们会用两种不同的方法实现。1,模块化设计:在之前的实验中我们做了3-8译码器和时钟分频,如果把这两个结合起来,我们就能搭建一个自动操作的流水LED显示。框图如下:2,循环赋值:这是一种很简洁的实现流水灯效果逻辑,就是定义一个8位的变量,在每个时钟上升沿将最低位赋值给最高

- 关键字: 流水灯 FPGA Lattice Diamond 小脚丫

Lattice MXO2: LED流水灯

- 在时钟分频实验中我们练习了如何处理时钟,接下来我们要学习如何利用时钟来完成时序逻辑。硬件说明流水灯实现是很常见的一个实验,虽然逻辑比较简单,但是里面也包含了实现时序逻辑的基本思想。要用FPGA实现流水灯有很多种方法,在这里我们会用两种不同的方法实现。1,模块化设计:在之前的实验中我们做了3-8译码器和时钟分频,如果把这两个结合起来,我们就能搭建一个自动操作的流水LED显示。框图如下:2,循环赋值:这是一种很简洁的实现流水灯效果逻辑,就是定义一个8位的变量,在每个时钟上升沿将最低位赋值给最高位,其他位右移一

- 关键字: 流水灯 FPGA Lattice Diamond 小脚丫

Altera MAX10: 时钟分频

- 时钟分频在之前的实验中我们已经熟悉了小脚丫的各种外设,掌握了verilog的组合逻辑设计,接下来我们将学习时序逻辑的设计。====硬件说明====时钟信号的处理是FPGA的特色之一,因此分频器也是FPGA设计中使用频率非常高的基本设计之一。一般在FPGA中都有集成的锁相环可以实现各种时钟的分频和倍频设计,但是通过语言设计进行时钟分频是最基本的训练,在对时钟要求不高的设计时也能节省锁相环资源。在本实验中我们将实现任意整数的分频器,分频的时钟保持50%占空比。1,偶数分频:偶数倍分频相对简单,比较容易理解。通

- 关键字: 时序逻辑 时钟分频 FPGA Lattice Diamond 小脚丫

Lattice MXO2: 时钟分频

- 时钟分频在之前的实验中我们已经熟悉了小脚丫的各种外设,掌握了verilog的组合逻辑设计,接下来我们将学习时序逻辑的设计。硬件说明时钟信号的处理是FPGA的特色之一,因此分频器也是FPGA设计中使用频率非常高的基本设计之一。一般在FPGA中都有集成的锁相环可以实现各种时钟的分频和倍频设计,但是通过语言设计进行时钟分频是最基本的训练,在对时钟要求不高的设计时也能节省锁相环资源。在本实验中我们将实现任意整数的分频器,分频的时钟保持50%占空比。1,偶数分频:偶数倍分频相对简单,比较容易理解。通过计数器计数是完

- 关键字: 时序逻辑 时钟分频 FPGA Lattice Diamond 小脚丫

Altera MAX10: 2位7段数码管显示

- 数码管显示本实验将会让你熟悉小脚丫上最后一种有意思的外设七段数码管。====硬件说明====数码管是工程设计中使用很广的一种显示输出器件。一个7段数码管(如果包括右下的小点可以认为是8段)分别由a、b、c、d、e、f、g位段和表示小数点的dp位段组成。实际是由8个LED灯组成的,控制每个LED的点亮或熄灭实现数字显示。通常数码管分为共阳极数码管和共阴极数码管,结构如下图所示:图1 共阳极、共阴极数码管共阴8段数码管的信号端低电平有效,而共阳端接高电平有效。当共阳端接高电平时只要在各个位段上加上相应的低电平

- 关键字: 数码管 FPGA Lattice Diamond 小脚丫

Lattice MXO2: 2位7段数码管显示

- 数码管显示本实验将会让你熟悉小脚丫上最后一种有意思的外设七段数码管。硬件说明数码管是工程设计中使用很广的一种显示输出器件。一个7段数码管(如果包括右下的小点可以认为是8段)分别由a、b、c、d、e、f、g位段和表示小数点的dp位段组成。实际是由8个LED灯组成的,控制每个LED的点亮或熄灭实现数字显示。通常数码管分为共阳极数码管和共阴极数码管,结构如下图所示:图1 共阳极、共阴极数码管共阴8段数码管的信号端低电平有效,而共阳端接高电平有效。当共阳端接高电平时只要在各个位段上加上相应的低电平信号就可以使相应

- 关键字: 数码管显示 FPGA Lattice Diamond 小脚丫

Altera MAX10: 3-8译码器

- 在这个实验里我们将学习如何用Verilog来实现组合逻辑。====硬件说明====组合逻辑电路是数字电路的重要部分,电路的输出只与输入的当前状态相关的逻辑电路,常见的有选择器、比较器、译码器、编码器、编码转换等等。在本实验里以最常见的3-8译码器为例说明如何用Verilog实现。3-8译码器的真值表如下:从前面的实验可以知道,当FPGA输出信号到LED为高电平时LED熄灭,反之LED变亮。同时我们可以以开关的信号模拟3-8译码器的输入,这样控制开关我们就能控制特定的LED变亮。====Verilog代码=

- 关键字: 组合逻辑 FPGA Lattice Diamond Verilog

Lattice MXO2: 3-8译码器

- 在这个实验里我们将学习如何用Verilog来实现组合逻辑。硬件说明组合逻辑电路是数字电路的重要部分,电路的输出只与输入的当前状态相关的逻辑电路,常见的有选择器、比较器、译码器、编码器、编码转换等等。在本实验里以最常见的3-8译码器为例说明如何用Verilog实现。3-8译码器的真值表如下:从前面的实验可以知道,当FPGA输出信号到LED为高电平时LED熄灭,反之LED变亮。同时我们可以以开关的信号模拟3-8译码器的输入,这样控制开关我们就能控制特定的LED变亮。Verilog代码// *****

- 关键字: 组合逻辑 FPGA Lattice Diamond Verilog

Altera MAX10: 点亮RGB三色灯

- 在这个实验里我们将学习控制小脚丫STEP-MAX10上的RGB三色LED的显示,基本的原理和点亮LED是相似的。====硬件说明====STEP-MXO2 V2开发板上面有两个三色LED,我们也可以用按键或者开关控制三色LED的显示。这是开发板上的2个三色LED,采用的是共阳极的设计,RGB三种信号分别连接到FPGA的引脚,作为FPGA输出信号控制。当FPGA输出低电平时LED变亮,当FPGA输出高电平时LED熄灭,当两种或者三种颜色变亮时会混合出不同颜色,一共能产生8种颜色。====Verilog代码=

- 关键字: 三色RGBLED FPGA Lattice Diamond 小脚丫

Lattice MXO2: 点亮RGB三色灯

- 在这个实验里我们将学习控制小脚丫STEP-MXO2上的RGB三色LED的显示,基本的原理和点亮LED是相似的。硬件说明STEP-MXO2 V2开发板上面有两个三色LED,我们也可以用按键或者开关控制三色LED的显示。这是开发板上的2个三色LED,采用的是共阳极的设计,RGB三种信号分别连接到FPGA的引脚,作为FPGA输出信号控制。当FPGA输出低电平时LED变亮,当FPGA输出高电平时LED熄灭,当两种或者三种颜色变亮时会混合出不同颜色,一共能产生8种颜色。Verilog代码// ******

- 关键字: 三色RGBLED FPGA Lattice Diamond 小脚丫

Altera MAX10: 点亮LED灯

- 恭喜你拿到我们的小脚丫开发板,在这个系列教程里你将更深入学习FPGA的设计同时更深入了解我们的小脚丫。如果你还没有开始使用小脚丫,也可以从这里一步一步开始你的可编程逻辑学习。请先准备好软硬件文档,因为FPGA的设计是和硬件息息相关,会经常用到这些文档。你还必须先安装好Quartus Prime设计工具,这是用小脚丫STEP-MAX10必须用到的。 硬件说明STEP-MAX10开发板虽然很小巧,上面也集成了不少外设,在本实验里我们就看看如何用FPGA控制简单外设,如何用按键或者开关控制LED的亮和

- 关键字: LED FPGA Lattice Diamond 小脚丫

Lattice MXO2: 点亮LED灯

- 恭喜你拿到我们的小脚丫开发板,在这个系列教程里你将更深入学习FPGA的设计同时更深入了解我们的小脚丫。如果你还没有开始使用小脚丫,也可以从这里一步一步开始你的可编程逻辑学习。请先到云盘准备好软硬件文档,因为FPGA的设计是和硬件息息相关,会经常用到这些文档。你还必须先安装好Diamond设计工具,这是用小脚丫STEP-MXO2必须用到的。1. 硬件说明STEP-MXO2 V2开发板虽然很小巧,上面也集成了不少外设,在本实验里我们就看看如何用FPGA控制简单外设,如何用按键或者开关控制LED的亮和灭。这是开

- 关键字: LED FPGA Lattice Diamond 小脚丫

lattice介绍

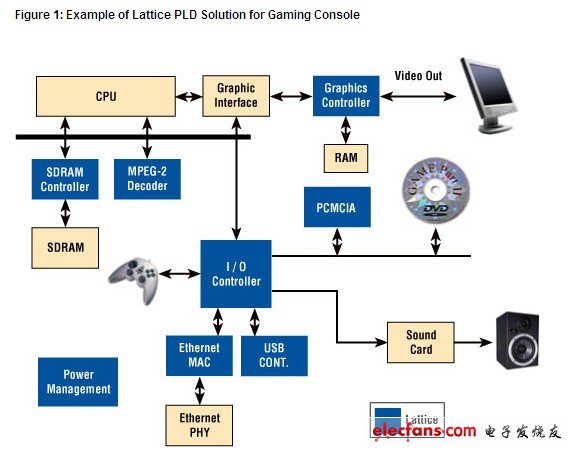

莱迪思(Lattice)半导体公司提供业界最广范围的现场可编程门阵列(FPGA)、可编程逻辑器件(PLD)及其相关软件,包括现场可编程系统芯片(FPSC)、复杂的可编程逻辑器件(CPLD),可编程混合信号产品(ispPAC?)和可编程数字互连器件(ispGDX?)。莱迪思还提供业界领先的SERDES产品。 FPGA和PLD是广泛使用的半导体元件,最终用户可以将其配置成特定的逻辑电路,从而缩短设 [ 查看详细 ]