fpga-to-asic 文章 最新资讯

基于FPGA的数字视频转换接口的设计与实现

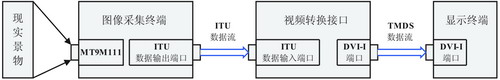

- 引言 本文从实际应用的角度出发,采用FPGA作为主控芯片,设计了一款数字视频接口转换设备,该设备针对于MT9M111这款数字图像传感器产生的ITU-R BT.656格式数据进行采集、色彩空间变换、分辨率转换等操作,完成了从ITU-R BT.656格式数据到DVI格式数据的转换,使得MT9M111数字图像传感器的BT656数据格式图像能够以1280×960(60Hz)和1280×1024(60Hz)两种显示格式在DVI-I接口的显示器上显示,并且还具有图像静止功能,在系统空

- 关键字: FPGA 数字视频 接口 传感器

基于FPGA的数字视频转换接口的设计与实现

- 引言 本文从实际应用的角度出发,采用FPGA作为主控芯片,设计了一款数字视频接口转换设备,该设备针对于MT9M111这款数字图像传感器产生的ITU-R BT.656格式数据进行采集、色彩空间变换、分辨率转换等操作,完成了从ITU-R BT.656格式数据到DVI格式数据的转换,使得MT9M111数字图像传感器的BT656数据格式图像能够以1280×960(60Hz)和1280×1024(60Hz)两种显示格式在DVI-I接口的显示器上显示,并且还具有图像静止功能,在系统空

- 关键字: FPGA

利用SmartCompile和赛灵思的设计工具进行设计保存

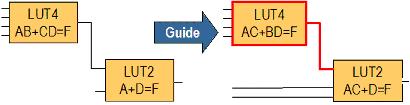

- 在FPGA环境下,设计保存实施比较复杂,需要保存的事项包括:一项设计的HDL描述、一个模块的综合网表、约束文件内的布局信息,以及在局部比特文件中的配置数据。赛灵思集成软件环境(ISE) 9.1i 软件以新的SmartCompile 技术为特色,其中包含两种新的方法:SmartGuide和Partitions,这两种方法可以保存像布局或布线这样的设计执行数据,并且可以减少解决问题所花费的时间。 SmartGuide采用命名和拓朴匹配技术来识别一个FPGA设计中相对于以前的实现还没有发生改变的各个部

- 关键字: FPGA

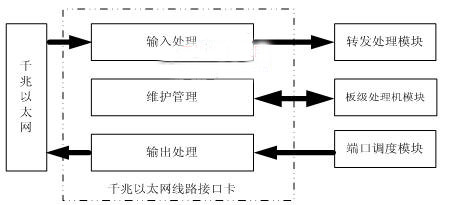

基于PM3388和FPGA的网络接口设计

- 本文根据十接口千兆以太网线路接口卡设计的功能需求和性能需求,按照数据处理流程划分功能模块,以PM3388作为链路层处理芯片和两片高性能FPGA作为链路层处理芯片完成了系统设计,并给出了具体实现方案。对两片FPGA控制功能的实现做了重点阐述,对实现难点做了深入的分析。 1 前言 随着网络规模的持续膨胀和新型网络应用需求的不断增长,目前基于IPv4技术的因特网在可扩展性、IP地址空间、安全、服务质量控制、移动性、运营管理和盈利模式等诸多方面面临着挑战,尤其是地址空间匮乏、可扩展性差等缺陷严重制

- 关键字: FPGA

利用FPGA协处理提升无线子系统的性能

- 您可以显著提高无线系统中信号处理功能的性能。怎样提高呢?有效方法是利用FPGA结构的灵活性和目前受益于并行处理的FPGA架构中的嵌入式DSP模块。 常见于无线应用中这类处理包括有限冲激响应(FIR)滤波、快速傅里叶变换(FFT)、数字上下变频和前向误差校正(FEC)。Xilinx? Virtex-4和Virtex-5架构提供多达512个并行嵌入式DSP乘法器,这些乘法器的工作频率高于500MHz,最高可提供256 GMAC的DSP性能。 将需要高速并行处理的工作卸载给FPGA,而将需要高速

- 关键字: FPGA

ARM、DSP、FPGA的特点和区别

- ARM(Advanced RISC Machines)是微处理器行业的一家知名企业,设计了大量高性能、廉价、耗能低的RISC处理器、相关技术及软 件。ARM架构是面向低预算市场设计的第一款RISC微处理器,基本是32位单片机的行业标准,它提供一系列内核、体系扩展、微处理器和系统芯片方案,四 个功能模块可供生产厂商根据不同用户的要求来配置生产。由于所有产品均采用一个通用的软件体系,所以相同的软件可在所有产品中运行。目前ARM在手持设备 市场占有90以上的份额,可以有效地缩短应用程序开发与测试的时间,也降低了

- 关键字: ARM DSP FPGA 特点 区别

基于FPGA的USB2.0虚拟逻辑分析仪的设计与实现

- 引言 传统的逻辑分析仪体积庞大、价格昂贵、通道数目有限,并且在数据采集、传输、存储、显示等方面存在诸多限制,在很大程度上影响了其在实际中的应用。选用高性能的FPGA芯片进行数据处理,充分利用PC的强大处理功能,配合LabView图形化语言开发的虚拟逻辑分析仪,其数据处理和传输速率大大提高,适用性极大增强,其显示、操作界面和低廉的成本较之传统的逻辑分析仪具有极大的优势和发展前景。 工作原理 本设计选用Altera公司的Cyclone系列FPGA器件EP1C3进行数据采集和处理,外接SR

- 关键字: FPGA

基于FPGA的键盘扫描模块的设计与实现

- 在电子产品中,键盘是最基本的输入设备,然而在应用中都采用通用的键盘扫描器件是不现实的,需要单独设计成专用的小键盘。现代EDA(电子设计自动化)技术提供了一种很好的途径,利用VHDL硬件描述语言和FPGA器件可以很方便地构建键盘扫描模块。经过实际操作检验,该模块可以很好地对每一次按键动作进行扫描和响应,实现预先设计的功能。 1 概述 1.1 通用键盘和专用键盘 在现代个人计算机系统中,一般都采用通用的标准键盘(如:标准101/102键盘或Microsoft自然PS/2键盘)来实现人与计

- 关键字: FPGA

PLD/FPGA新手入门

- PLD是可编程逻辑器件(Programable Logic Device)的简称,FPGA是现场可编程门阵列(Field Programable Gate Array)的简称,两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或PLD/FPGA。 PLD是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于70年代单片机的发明和使用。 PLD能做什么呢?可以毫不夸张的讲,PLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74

- 关键字: PLD FPGA 入门

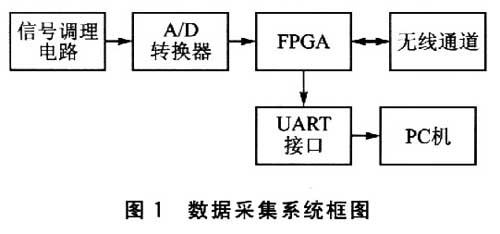

ADS8344和FPGA的高精度数据采集前端

- 数据采集在工业测试系统中是一个很重要的环节,其精确性和可靠性是至关重要的。本文阐述的数据采集系统精度高达16位,能够对8个外部模拟通道进行A/D采样,最大模拟输入信号范围达到-15~+15V。该系统具有限幅保护功能,程序编写简便,能够实现对远端数据的采集和传输。 1 系统硬件设计 数据采集系统框图如图1所示。 图中,A/D转换器采用了TI公司的16位逐次逼近型ADS8344;FPGA主要用于控制ADC的启动、停止和查询ADC状态等,同时对数据进行高速数据缓

- 关键字: ADS8344 FPGA 数据采集

基于FPGA和DSP的高速瞬态信号检测系统

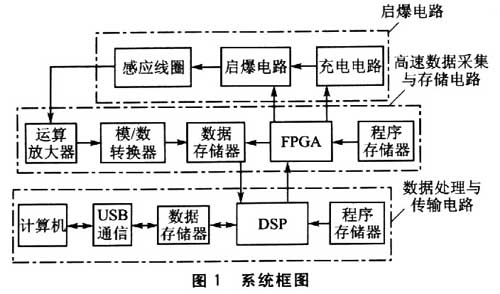

- 引 言 目前国内急需一种能够对电火工品的发火过程进行实时无损耗监测的方法和手段,并根据监测结果对火工品的可靠性进行准确的判决和认证,解决科研和生产过程中的具体问题。本系统采用感应式线圈作为非接触式启爆电流的启爆装置,并采用高速A/D、FPGA、DSP等先进的集成电路实现了电火工品的无损耗检测。其主要目的是:第一,解决电火工品可靠性试验中微秒级瞬态信号的检测、处理和存储技术;第二,为可靠性试验提供一种在线的无损耗实时检测系统,以便对电火工品的发火全过程进行监测;第三,为电火工品的发火可靠性认证和评

- 关键字: FPGA DSP A/D

使用VHDL语言设计FPGA的几个常见问题的探讨

- 详细讨论了在MAX plusⅡ开发平台下使用VHDL硬件描述语言设计现场可编程门阵列(FP-GA)时常见的三个问题:等占空比分频电路、延时任意量的延时电路、双向电路。 1 引言 随着EDA技术的发展,使用硬件语言设计可编程逻辑器件(PLD)/现场可编程门阵

- 关键字: VHDL FPGA 问题

fpga-to-asic介绍

您好,目前还没有人创建词条fpga-to-asic!

欢迎您创建该词条,阐述对fpga-to-asic的理解,并与今后在此搜索fpga-to-asic的朋友们分享。 创建词条

欢迎您创建该词条,阐述对fpga-to-asic的理解,并与今后在此搜索fpga-to-asic的朋友们分享。 创建词条