- 由于经济下滑损及开发预算减少,嵌入系统设计者正在转向FPGA(现场可编程门阵列)技术,以缩减开发周期、对抗设备老化以及简化产品升级。通过采用数量庞大且不断增加的FPGA开发工具、可重用逻辑单元以及市售商用模块,设计者可以构思出高性能嵌入系统,并且能够根据需求变化作重新配置,从而尽量减少对工程和制造的影响。过去,电路板设计者使用这些器件作系统元件之间的互连,但最新的高密度产品也可以替代一个典型嵌入项目中的处理器、内存、定制逻辑及很多外设。尽管它有能力改变嵌入架构,设计者仍应分析性能、功率和成本局限,以确

- 关键字:

Xilinx FPGA

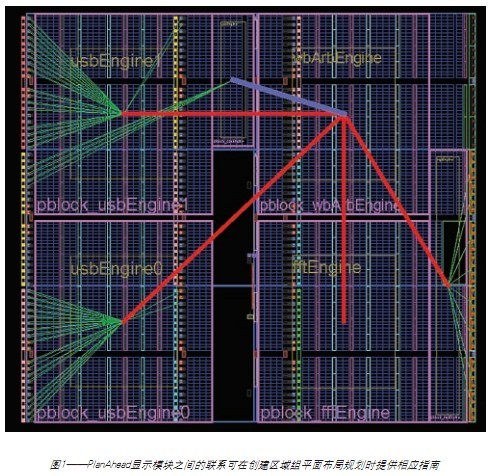

- 在FPGA中植入嵌入式系统,如今,由于可编程器件(如FPGA)容量大、性能高、成本相对较低的特性,这种平衡又在发生变化,以前硬件设计元素(如处理器及其外围器件和逻辑块)也可以转移到软领域(图1)。因此,在整个开发周期内,灵活性可能更大,更改

- 关键字:

系统 嵌入式 植入 FPGA

- 摘 要: 以Altera公司MAX7000系列为代表,介绍了CPLD在DSP系统中的应用实例。该方案具有一定的普遍适用性。

关键词: RESET BOOT HPI CPLD的延时 时序 DSP的速度较快,要求译码的速度也必须较快。利用

- 关键字:

CPLD DSP 系统 中的应用

- 摘要:设计了以FPGA为核心采集模块,以单片机为显示控制核心,以TFT彩屏液晶为显示器件的便携数字存储示波器。通过异步FIFO实现了FPGA中高速数据流与单片机处理速度之间的速率匹配。以三总线结构以及控制信号的握手协

- 关键字:

FPGA TFT 彩屏 便携

- 近日Altera公司、MIPS科技公司以及System Level Solutions (SLS) 公司联合推出了MIPS-Based™、FPGA优化软核处理器,适用于Altera FPGA以及ASIC器件。MP32处理器是MIPS®兼容应用类处理器,继承了业界规模最大的软件开发工具以及操作系统支持生态系统。MP32处理器是业界第一款基于FPGA的软核处理器,由Wind River公司的VxWorks RTOS和MIPS Navigator ICS软件开发套装提供支持。

- 关键字:

Altera FPGA

- 工程师在设计过程中,经常需要一定的创造力(你不妨称之为数字管道胶带)才能够保证设计的顺利完成。过去8年时间里,我曾经目睹许多优秀工程师利用这一方法出色地完成了许多工作,而他们采用的最主要工具就是 FPGA Editor。

利用FPGA Editor,你可以察看完成的设计并确定是否在FPGA构造一级真正实现了设计意图 – 而这对于任何工程师或现场应用工程师来说都是非常需要的。假设你拿到协作者的设计,需要对其进行修改,但他们的 HDL源代码非常难于理解,或者根本没有任何注释或文档。也许你

- 关键字:

Xilinx FPGA 设计工具

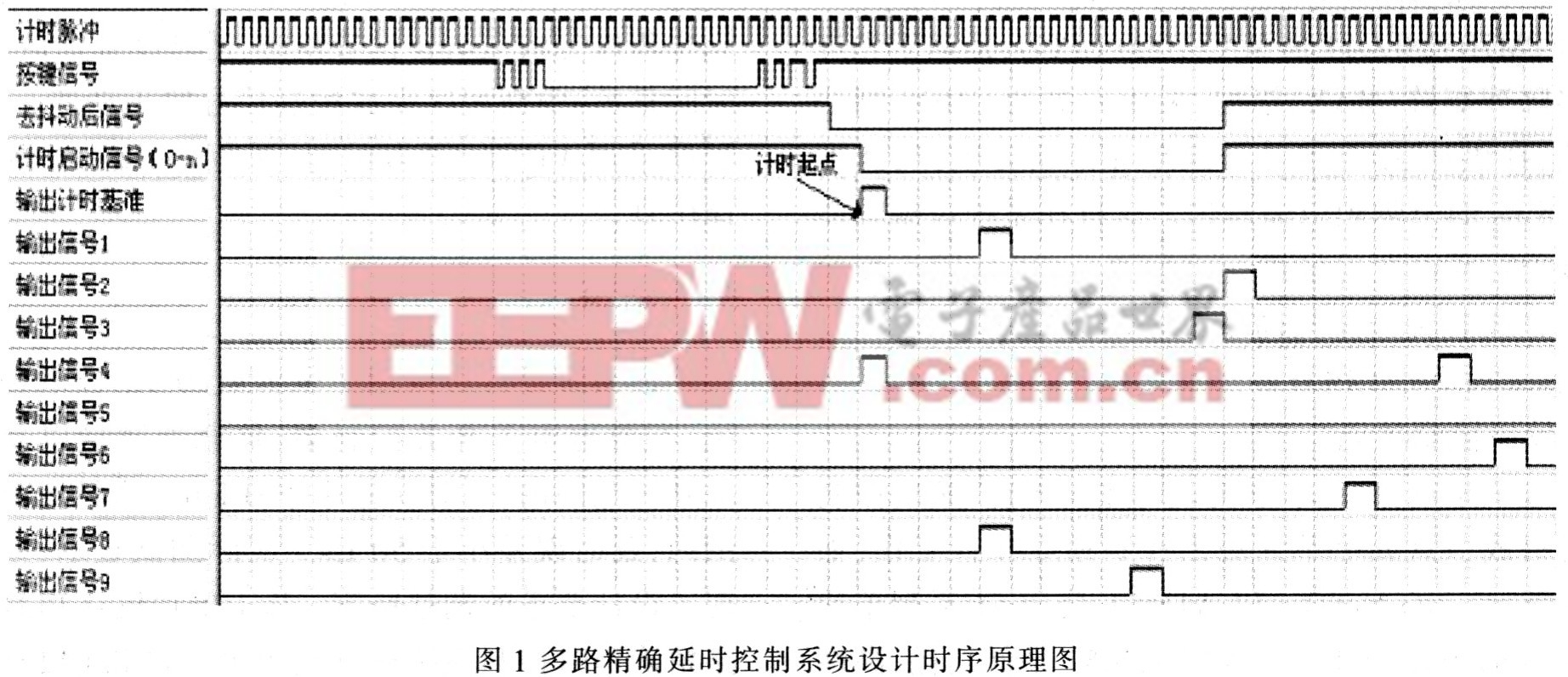

- 1 引言

现代控制系统中控制对象可能是复杂、分散的,而且往往是并行、独立工作的,但整体上它们是相互关联的有机组合。因此,控制信号的时序逻辑则要求更加精确。CPLD单片机为控制系统提供了技术支持,由CPLD和

- 关键字:

控制系统 延时 精确 CPLD 单片机

- 近几年来,电线、电缆、光纤等产品的需求量大大增加,外径尺寸的质量控制成为许多生产厂家急需解决的问题。传统 ...

- 关键字:

ARM FPGA 线阵CCD测径系统

- LSI接口终于要实现“光纤”化了。美国阿尔特拉(Altera)公布了在FPGA中导入光纤接口的计划。预定在2011年内采用试制芯片进行演示,2012年以后产品化。产品主要面向高清视频传输、云计算、三维游戏以及高性能视频监控等用途。在这些产品中,除了主板上的LSI间布线外,还可广泛地用于机壳内布线等用途。

- 关键字:

Altera FPGA

- 摘要:基于提高速度和减少面积的理念,对传统的FIR数字滤波器进行改良。考虑到FPGA的实现特点,研究并设计了采用Radix-2的Booth算法乘法器以及结合了CSA加法器和树型结构的快速加法器,并成功应用于FIR数字滤波器的设

- 关键字:

FPGA FIR 数字滤波器

- 过去,FPGA在系统设计中发挥了重要作用,但现在还需要新的性能,同时需要降低整个系统的构建和运营成本。功能丰富、低成本的FPGA实现了快速的产品上市时间与较短的投资回报周期,并且拥有能够适应不断发展的标准的灵活性和性能。系统/设计工程师现在还拥有了一个令人兴奋的、改进的工具集来解决不断演进的信号处理市场的挑战。

- 关键字:

RapidIO FPGA 串行 低功耗

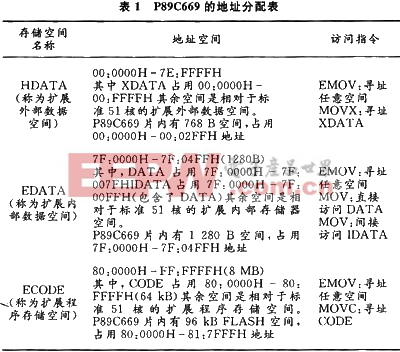

- 利用P89C669的23 b的线性地址并采用CPLD外部扩展,采用CPLD增强单片机P89C669外部设备扩展能力 2007.08.15 来自:现代电子技术 P89C669是PHILIPS半导体一款51MX(存储器扩展)内核的微处理器,其指令执行速度2倍于标准的80C51器件,线性地址经扩展后可支持高达8 MB的

- 关键字:

CPLD 外部 扩展 采用 地址 P89C669 线性 利用

- FPGA在嵌入式系统中的开发方向,早期的嵌入式系统一般是以通用处理器或单片机为核心,在外围电路中加入存储器、功率驱动器、通信接口、显示接口、人机输入接口等外围接口,再加上应用软件,有些还加上了嵌入式操作系统,从而构成完整的系统。 随

- 关键字:

方向 开发 系统 嵌入式 FPGA

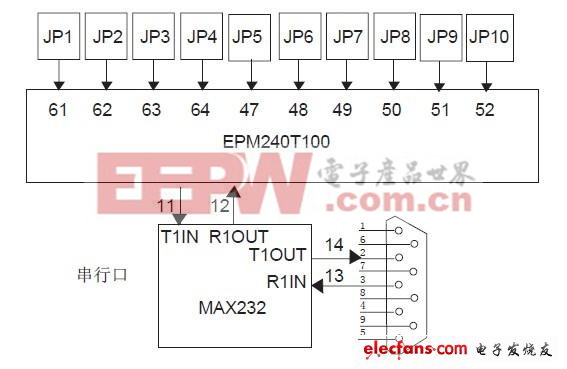

- 一、硬件电路设计 本文选用CPLD 是ALTERA 公司的EPM240T100,结合MAX232 接口芯片进行串口通信设计,框图如下图1 所示。 图1 CPLD串口通信模块硬件设计 二、VHDL程序模块设计及描述 使用VHDL 对CPL

- 关键字:

设计 通信 串口 CPLD

- 满足设计的时序要求本身已非易事,而要实现某项设计的整体时序具有完全可重复性有时候却是不可能的任务。幸运的是,设计人员可以借助有助于实现可重复时序结果的设计流程概念。影响最大的四个方面分别是 HDL 设计实践、综合优化、平面布局和实施方案。

就获得可重复结果而言,资源利用和频率要求都很高的设计是最大的挑战。它们也是可重复结果流程需求最高的设计。得到可重复结果的第一步是在 HDL设计阶段运用设计合理的实践。遵循出色的分层边界实践有助于保持逻辑整体性,而这在设计变更时有助于保持可重复结果。一条不错的规

- 关键字:

Xilinx FPGA

fpga-cpld介绍

您好,目前还没有人创建词条fpga-cpld!

欢迎您创建该词条,阐述对fpga-cpld的理解,并与今后在此搜索fpga-cpld的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473