- 引言

误码仪是评估信道性能的基本测量仪器。本文介绍的误码仪结合FPGA 的特点,采用全新的积分式鉴相结构,提出了一种新的误码测试方法,经多次测试验证,方案可行,设计的系统稳定。本文设计的误码仪由两部分组成:发信机和接收机。

1 发信机

发信机的主要功能是产生具有随机特性的伪随机m 序列,通过FPGA 由VHDL 编程实现。伪随机序列产生原理如下:

图1 伪随机序列产生原理图

其中,ak-i是各移位寄存器的状态,Ci对应各寄存器的反馈系数,为1表示参与反馈

- 关键字:

FPGA 测试仪 VHDL MCU和嵌入式微处理器

- 嵌入式系统与桌面PC结构非常不同,但其底层技术发展却是一样的,而且遵循着类似发展趋势。当桌面PC转向64位架构来满足不断增长的存储器要求时,嵌入式系统也由于同样的原因快速转向32位处理器。桌面/服务器计算市场主要是围绕x86架构,大多数创新和差异都在系统级,如双核、四核或多核中央处理架构、集成图像处理器单元和存储器控制器等等。同样,嵌入式系统则主要围绕简单的32位RISC处理器,多核架构、集成外设以及可配置处理等系统级发展,使得设计人员能够快速适应不断变化的应用要求。

根据iSuppli的研究报

- 关键字:

嵌入式 FPGA 处理器 MCU和嵌入式微处理器

- Altera公司产品和企业市场副总裁DannyBiran

低功耗是一种战略优势

在器件的新应用上,FPGA功耗和成本结构的改进起到了非常重要的作用。Altera针对低功耗,同时对体系结构和生产工艺进行改进,使我们的高端StratixIIIFPGA能够用于高性能计算领域,而低成本CycloneIIIFPGA用于软件无线电,MaxIIZCPLD则适合便携式应用。

在生产工艺方面,Altera在很大程度上受益于和TSMC的合作。这种紧密的合作关系使Altera能够在CycloneIII中充

- 关键字:

处理器 FPGA CPLD 嵌入式

- 引言 从最初的计算机和电话开始,互联网络一直是电子工程的关键构成。在超大规模集成(VLSI)电路时代,由于MOS晶体管的驱动特性以及片内互联相对较大的电容,互联网络变得尤其重要。 芯片内部用于连接功能单元的互联网络对芯片性能有很大的影响,甚至是决定性的影响。总线虽然是一种最简单的互联,但从容量或者电源角度看,却是较差的选择,因为驱动总线以最大速率工作时需要的电源和空间随总线电容呈指数增大。而且,多点连接网络也不是一种好选择,因为即使每次只需要一次对话,或者会话限于最近的邻居之间,也

- 关键字:

FPGA IP 集成 对比 模拟技术 电源技术 模拟IC 电源

- 汽车制造商们坚持不懈地改进车内舒适性、安全性、便利性、工作效能和娱乐性,反过来,这些努力又推动了各种车内数字技术的应用。然而,汽车业较长的开发周期却很难跟上最新技术的发展,尤其是一直处于不断变化中的车内联网规范,以及那些来自消费市场的快速兴起和消失的技术,从而造成了较高的工程设计成本和大量过时。向这些组合因素中增加低成本目标、扩展温度范围、高可靠性与质量目标和有限的物理板空间,以及汽车设计中存在的挑战,最多使人进一步感到沮丧。可编程逻辑器件 (PLD),如现场可编程门阵列 (FPGA) 和复杂 PLD

- 关键字:

FPGA PLD SOC MCU和嵌入式微处理器

- 赛灵思宣布开始正式发放高性能计算行业首款针对Intel前端总线(FSB)的FPGA加速解决方案商业许可。基于高性能65nm Virtex™-5 平台 FPGA 和Intel® QuickAssist技术,赛灵思公司的加速计算平台(Accelerated Computing Platform, ACP)M1许可包支持实现全速1066MHz FSB性能。ACP M1许可包目前已开始向系统集成商提供,支持他们进行解决方案的开发,以提高基于Intel处理器的服务器平台的性能,并保证把功耗和

- 关键字:

赛灵思 FPGA Intel MCU和嵌入式微处理器

- 随着65nm工艺的应用以及更多低功耗技术的采用,FPGA拥有了更低的成本、更高的性能以及突破性的低耗电量,具备进入更广泛市场的条件。FPGA从业者表示,今年FPGA快速增长,而预计明年仍将是一个增长年。

比拼65nm器件 加快45nm研发

就像两三年前,可编程逻辑器件领域的两大厂商在90nm器件上进行大比拼一样,2007年,这两家企业Xilinx和Altera又在新一代技术节点65nm器件上开始了竞赛。一方面Xilinx宣称他们比竞争对手领先推出了65nm器件,另一方面Altera则在宣布

- 关键字:

65nm FPGA DSP MCU和嵌入式微处理器

- Altera计划2008年推出45nm产品。45nm工艺可以为客户带来价值,但是提高了厂商进入的门槛,使45nm是重量级厂商才能玩得起的游戏。45nm使FPGA有更多的机会进入ASIC领域,因ASIC的开发风险更高。45nm开发的三要素是:选择正确的合作伙伴;投片的第一个硅片就可以交付给用户;IC设计和生产紧密合作。

45nm芯片性能更高

从技术演化图的发展可知,十年来,半导体业每两年推出一个新的工艺节点,这种趋势还将继续保持着,并向35nm、22nm节点推进。其背后的驱动力来自于成本降低

- 关键字:

0712_A 杂志_市场纵横 Altera 45nm FPGA MCU和嵌入式微处理器

- 半导体业最主要的特征是工艺尺寸不断进步,平均每2~3年就要升级一次,带动功耗和成本不断下降、性能提升。从180nm到130nm,再到90nm、65nm和45nm…,这些略显枯燥的数字使我们的生活正在加速进入数字时代。当工艺进入65nm时代,FPGA厂商收获的不仅仅是关注的目光,更是新的机遇。

众所周知,通信、仪器、工业、军工、航天等市场具有小批量、多品种的特点,如果投入大量资源开发一种专用的芯片,经济上不划算。另外,越来越多的企业意识到差异化的快速灵活生产才是发展之道,但ASIC高昂的芯片设计和

- 关键字:

0712_A 杂志_技术长廊 FPGA 65nm MCU和嵌入式微处理器

- 在图像通信、遥感图像分析、医学成像诊断等应用领域,为了便于显示、观察或进行进一步的处理,常常需要对原始的数字图像进行特征提取(如边缘检测、边缘锐化)、噪声平滑滤波、几何校正等处理,这类图像处理技术称为图像的预处理。在实际应用中,空域滤波算法被广泛地应用于图像的预处理技术中。

空域滤波算法是图像增强技术的一种,直接对图像的象素进行处理,不需要进行变换。常见的滤波算子如锐化算子、高通算子、平滑算子等,可以完成图像的边缘提取、噪声去除等处理。这些滤波算子尽管功能不同,实现方法却都是类似的,都是通过模板

- 关键字:

数字图像 滤波 FPGA MCU和嵌入式微处理器

- 随着65nm工艺的应用以及更多低功耗技术的采用,FPGA拥有了更低的成本、更高的性能以及突破性的低耗电量,具备进入更广泛市场的条件。FPGA从业者表示,今年FPGA快速增长,而预计明年仍将是一个增长年。

比拼65nm器件 加快45nm研发

就像两三年前,可编程逻辑器件领域的两大厂商在90nm器件上进行大比拼一样,2007年,这两家企业Xilinx和Altera又在新一代技术节点65nm器件上开始了竞赛。一方面Xilinx宣称他们比竞争对手领先推出了65nm器件,另一方面Altera则在

- 关键字:

FPGA 65nm 低功耗 嵌入式

- 摘要: 本文介绍了AD9271在全数字超声系统上的应用。

关键词: AD9271;FPGA;SPI

前言

随着电子计算机、现代信号处理技术的不断发展,超声成像系统逐渐向全数字化方向发展。全数字超声成像技术在接收前端将回波信号转变为数字量,通过设计专用ASIC系统替代传统模拟处理电路,实现信号的延迟、叠加及信号处理,使图像更清晰、更准确,分辨率更高,提高了超声诊断设备的质量。

AD9271是ADI公司针对全数字超声系统推出的8通道单芯片模拟前端。其极高的集成度允许医疗设备设计师将

- 关键字:

AD9271 FPGA SPI 0712_A 杂志_设计天地 模拟IC 音视频技术

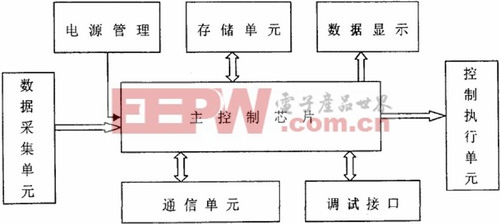

- 由于各种原因,公交车总是不断重复加速―减速或停车―再加速的过程。通过加装本节能装置,当汽车需要制动时,在主控单元的控制下,可将汽车行驶时具有的巨大动能通过空气压缩机转化成高压气体的势能并储存起来,从而实现汽车减速或停车。

- 关键字:

控制系统 节能 汽车 嵌入式 ARM

- ACTEL推出全新Icicle 工具套件,进一步彰显业界最低功耗现场可编程门阵列 (FPGA) 在便携式解决方案中的优势。新工具套件充分利用Actel的5微瓦 (µW) IGLOO™ FPGA,展现了IGLOO在便携式应用中的超低功耗特性、灵活的实现方案选项和节省电池能量的优势。该套件可让设计人员轻松且快速地对其基于IGLOO的低功耗便携式设计进行编程、评估和修改。其中,1.4” x 3.6”的 Icicle评测板由可充电的锂离子电池供电,在纤小型手机设计中,其功耗低至其它竞争

- 关键字:

ACTEL FPGA Icicle MCU和嵌入式微处理器

fpga+arm介绍

您好,目前还没有人创建词条fpga+arm!

欢迎您创建该词条,阐述对fpga+arm的理解,并与今后在此搜索fpga+arm的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473