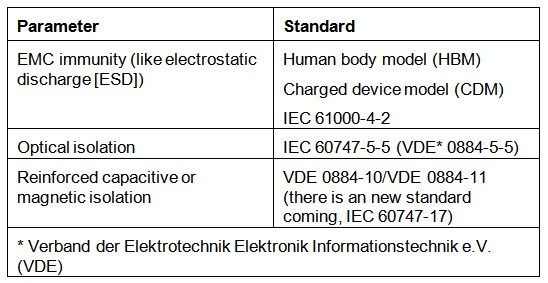

- 一、EMC定义EMC:EMC(electromagnetic compatibility)电磁兼容,是系统能完全正常工作的能力(性能不降级)。在正常环境中,电磁兼容要求设备或系统既不受周围电磁场的干扰而失常,又不会产生电磁干扰影响其他设备。EMS:EMS(electromagnetic susceptibility)电磁耐受性,是设备或系统对噪声干扰的抗干扰能力。EMS 等级高则设备抗扰度好;相反 EMS 等级低的设备对电磁环境极其敏感,其工作状态受周围电磁环境影响。(所以很多地方将 electromag

- 关键字:

单片机 EMC

- 在提到干扰对USB的影响时,差分数据传输与简单的同轴电缆相比具有很大的优势。在感性干扰效应(磁场)情况下,导线的绞合可以弥补干扰效应。●USB控制器的输入/输出不是完全对称的,因此USB信号显示出共模干扰。●Layout与HF/EMC不兼容,寄生电容和缺少波阻匹配会产生共模干扰。●电路设计(USB滤波器)不充分,滤波器影响信号质量,和/或插损太低。●接口设计(插座,外壳)不充分。不良的接地会减小电缆的屏蔽衰耗。滤波器具有不良的接地参考。●USB电缆不对称、屏蔽不良以及没有足够好的接地。这种电缆会劣化信号质

- 关键字:

EMC 静电测试 USB

- 分享一个EMI整改文档,对于EMC来说,接触的案例越多,整改的成功率就越高,整改的方法也越多,从案例中吸取教训,总结经验,避免设计中出现同样的问题。注意:按照文档描述,从下面两张图片可以看出470MHz和940MHz(二次谐波)左右,这两个频点的功率非常高,可能该产品是一款无线产品,对于主频--有意辐射频率来说是有豁免权的,所以只需要注意200MHz之前的频段,由于频谱超标带宽较宽,可以肯定非时钟、晶振辐射超标引起,几乎肯定辐射源在电源了,不过最后的结果,电源部分虽然PASS了,但是后面又引起了其他的频点

- 关键字:

EMC 静电测试

- 在采样速率和可用带宽方面,当今的射频模数转换器(RF ADC)已有长足的发展,其中还纳入了大量数字处理功能,电源方面的复杂性也有提高。那么,RF ADC为什么有如此多不同的电源轨和电源域?为了解电源域和电源的增长情况,我们需要追溯ADC的历史脉络。早期ADC采样速度很慢,大约在数十MHz内,而数字内容很少,几乎不存在。电路的数字部分主要涉及如何将数据传输到数字接收逻辑——专用集成电路 (ASIC) 或现场可编程门阵列 (FPGA)。用于制造这些电路的工艺节点几何尺寸较大,约在180 nm或更大。使用单电压

- 关键字:

ADI RF ADC

- 近期,Guerrilla RF宣布收购了Gallium Semiconductor的GaN功率放大器和前端模块产品组合。Guerrilla RF表示,通过此次收购,公司获得了Gallium Semiconductor 所有现有的元件、正在开发的新内核以及相关知识产权(IP)。公司将为无线基础设施、军事和卫星通信应用开发新的GaN器件产品线并实现商业化。Guerrilla RF官方经销商Telcom International的一位员工表示,公司计划向韩国市场供应Guerrilla RF的射频晶体管,并将其

- 关键字:

Guerrilla RF Gallium GaN

- 6月14日,纯化合物半导体代工厂稳懋半导体(WIN Semiconductors Corp)宣布,公司扩大了其RF

GaN技术组合,推出了基于碳化硅(SiC)的毫米波氮化镓(GaN)技术测试版NP12-0B平台。目前,NP12-0B鉴定测试已经完成,最终建模/PDK生成预计将于2024年8月完成,并计划于2024年第三季度末发布完整的生产版本。据稳懋半导体介绍,该平台的核心是0.12μm栅极RF GaN

HEMT技术,该技术结合了多项改进,以增强直流和射频的耐用性,并增加芯片级防潮性。NP12-0

- 关键字:

纯化合物 半导体 RF GaN

- 在复杂的电磁环境中,每台电子、电气产品,除了本身要能抗住一定的外来电磁干扰,正常工作以外,还不能产生对该电磁环境中的其它电子、电气产品来说,所不能承受的电磁干扰。或者说,既要满足有关标准规定的电磁敏感度极限值要求,又要满足其电磁发射极限值要求,这就是电子、电气产品电磁兼容性应当解决的问题,也是电子、电气产品通过电磁兼容性认证的必要条件。很多工程师在进行产品电磁兼容性设计时,对于如何正确选择和使用电磁兼容性元器件,往往束手无策或效果不理想,因此,很有必要对此进行探讨。电磁兼容性元器件,是解决电磁干扰发射和电

- 关键字:

电磁兼容 EMC EMI 元器件 电路设计

- 1 层分布1.1 双面板,顶层为信号层,底面为地平面。1.2 四层板,顶层为信号层,第二层为地平面,第三层走电源、控制线。特殊情况下(如 射频信号线要穿过屏蔽壁),在第三层要走一些射频信号线。每层均要求大面积敷地。1.2 四层板,顶层为信号层,第二层为地平面,第三层走电源、控制线。特殊情况下(如 射频信号线要穿过屏蔽壁),在第三层要走一些射频信号线。每层均要求大面积敷地。2 接地地线设计在电子设备中,接地是控制干扰的重要方法。如能将接地和屏蔽正确结合起来使用,可解决大部分干扰问题。电子设备中地线结构大致有

- 关键字:

PCB EMC 设计

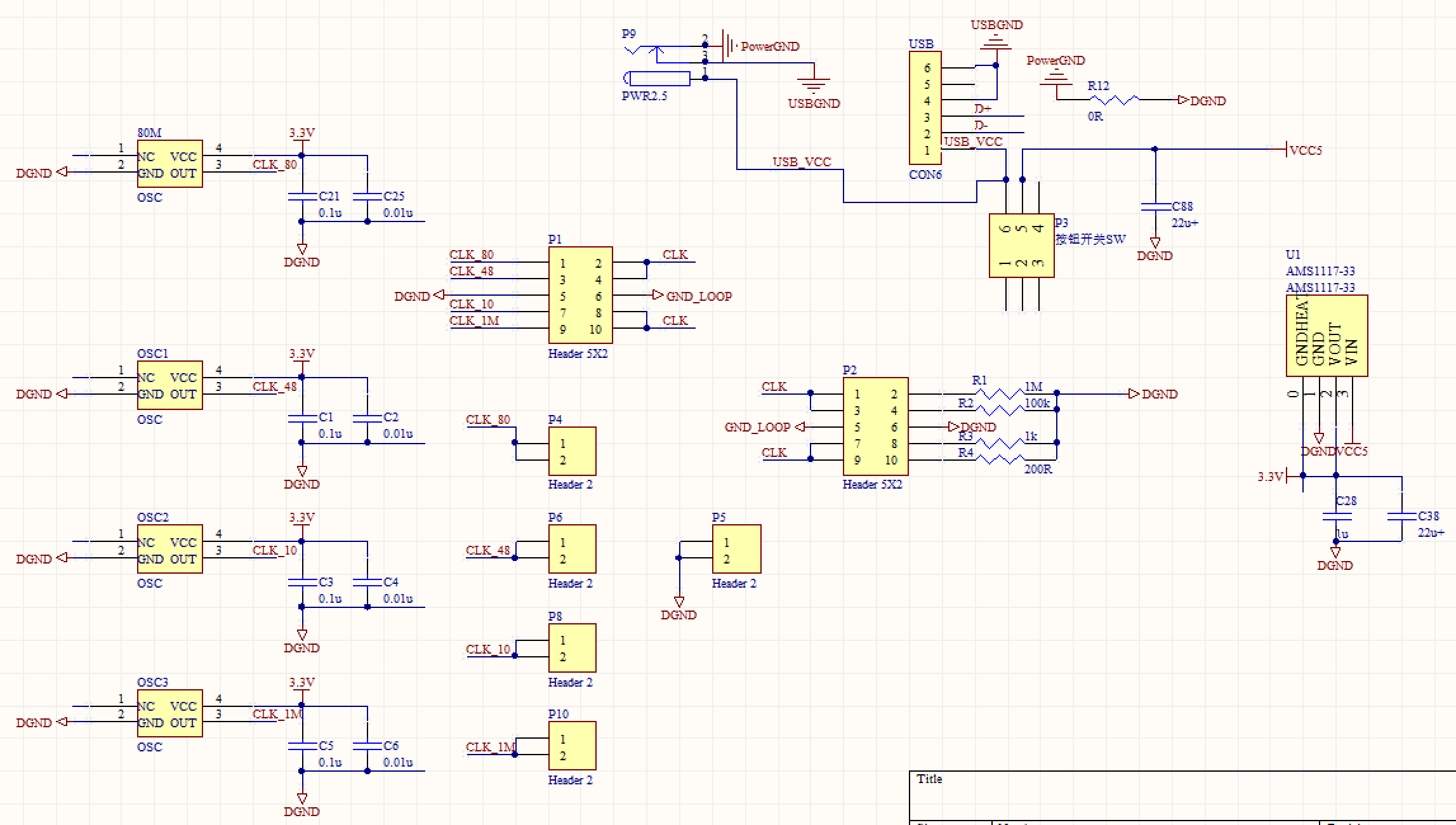

- EMC是一个棘手的问题,下面这个文章一定值得你看,从源头解决问题才是真正的解决问题。首先看定义,定义主要按照问题性质,分为电源、时钟CLK问题、地不平衡问题。再看原因分析:针对三种问题,小编都有举例分析。先看电源问题:1、排查手段2、问题分析一般电源问题为DC-DC电路器件(DC-DC芯片、电感、二极管)选型问题:一般电源问题为DC-DC PCB部分设计不合理问题:3、根源再看时钟问题:解决思路中的传统方案传统手段:硬件扩频:解决思路中的更换方案:地不平衡问题:最后,分析思路:EMC三大规律规律一:EMC

- 关键字:

EMC 静电测试

- 电子产品如手机,智能手表,TWS耳机在认证时往往需要做静电测试,测试过程出现不可恢复的故障,或整机复位重启。问题详细描述某智能手表在静电测试时,打充电输入端子的接触±4KV出现系统复位,甚至概率性卡死,长时间不能恢复。充电端子在bottom层,板子为四层一阶。问题具体分析1、分析如下:经过对PCB的研究发现,在充电弹片和正极充电路径下方的相邻层信号线过多,没有完整的地来释放静电,并有高速的flash信号经过。当静电打进来时,静电瞬间干扰到信号走线,静电管还来不及释放静电,导致系统异常。第四层(bottom

- 关键字:

EMC 静电测试

- 电磁干扰的三要素是干扰源、干扰传输途径、干扰接收器。EMC就围绕这些问题进行研究。最基本的干扰抑制技术是屏蔽、滤波、接地。它们主要用来切断干扰的传输途径。广义的电磁兼容控制技术包括抑制干扰源的发射和提高干扰接收器的敏感度,但已延伸到其他学科领域。本规范重点在单板的EMC设计上,附带一些必须的EMC知识及法则。在印制电路板设计阶段对电磁兼容考虑将减少电路在样机中发生电磁干扰。问题的种类包括公共阻抗耦合、串扰、高频载流导线产生的辐射和通过由互连布线和印制线形成的回路拾取噪声等。在高速逻辑电路里,这类问题特别脆

- 关键字:

EMC

- 前言:PCB设计时,需要考虑的一个最基本的问题就是实现电路要求的功能需要多少个布线层、接地平面和电源平面,PCB的叠层设计通常是在考虑各方面的因素后折中决定的。下面为你详解PCB叠层设计的原则性。1、叠层规划方案● 外层带有 GND 和 PWR 的堆叠主要用于扇出和短走线。对于 HDI 的目的,第二层是信号层,用于从细间距 BGA 中运行走线。在此 HDI 应用中,制造商将使用激光钻孔执行控制深度钻孔过程以访问第 2 层。● 所有叠层都需要从 PCB 结构中心线的层之间平衡层压板厚度,

- 关键字:

PCB设计 EMC PCB叠层

- 大家在画多层PCB的时候都要进行层叠的设置,其中层数越多的板子层叠方案也越多,很多人对多层PCB的层叠不够了解,通常一个好的叠层方案可以降低板子产生的干扰,我们的层叠结构是影响PCB板EMC性能的重要因素,下面我们以四层板和六层板为例介绍一下他们的层叠方案,让我们从中选出最优的层叠结构。其中四层板的层叠结构有如下三种第一种:第二种:第三种:我们首先分析一下第一种和第二种叠层,这两个叠层的区别时第二层和第三层相反,这两个也是四层板用的比较多的叠层方案,这两种叠层方案都是可行的,只是需要根据我们板子的实际情况

- 关键字:

PCB设计 EMC PCB叠层

- 在PCB的EMC设计考虑中,首先涉及的便是层的设置;单板的层数由电源、地的层数和信号层数组成;在产品的EMC设计中,除了元器件的选择和电路设计之外,良好的PCB设计也是一个非常重要的因素。PCB的EMC设计的关键,是尽可能减小回流面积,让回流路径按照我们设计的方向流动。而层的设计是PCB的基础,如何做好PCB层设计才能让PCB的EMC效果最优呢?今天,小编就和大家分享一下。一、PCB层的设计思路:PCB叠层EMC规划与设计思路的核心就是合理规划信号回流路径,尽可能减小信号从单板镜像层的回流面积,使得磁通对

- 关键字:

PCB设计 EMC

- 在低频下工作的普通电路与针对RF频率设计的电路之间的关键区别在于它们的电气尺寸。RF设计可采用多种波长的尺寸,导致电压和电流的大小和相位随元件的物理尺寸而变化。这为RF电路的设计和分析提供了一些基础的核心原理特性。基本概念和术语假设以任意负载端接传输线路(例如同轴电缆或微带线),并定义波量a和b,如图1所示。图1.以单端口负载端接匹配信号源的传输线路。这些波量是入射到该负载并从该负载反射的电压波的复振幅。我们现在可以使用这些量来定义电压反射系数Γ,它描述了反射波的复振幅与入射波复振幅的比值:反射系数也可以

- 关键字:

ADI RF 波反射

emc-rf介绍

您好,目前还没有人创建词条emc-rf!

欢迎您创建该词条,阐述对emc-rf的理解,并与今后在此搜索emc-rf的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473