- 摘 要: 介绍了基于Altera公司EP1K30TC144芯片的电梯控制器设计过程,描述了该控制系统的功能。该设计采用VHDL语言进行编程,以QUARTUSⅡ软件为开发平台,对本设计进行了仿真,并使用JTAG将程序代码下载到实验板上进行了硬件验证。

关键词: 电梯控制器; VHDL; EP1K30TC144; QUARTUSⅡ

随着社会的发展,电梯的使用越来越普遍,对电梯功能的要求也不断提高,相应地其控制方式也在不断发生变化。对于电梯的控制,传统的方法是使用继电器-接触器控制系

- 关键字:

Altera FPGA 芯片

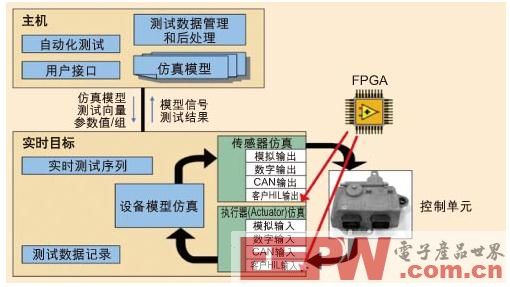

- 因为现场可编程门阵列(FPGA)技术具有自定义逻辑功能和高可靠性的特点,所以,工程师已将FPGA技术融入测试系统,解决汽车电子设计与测试的困难,同时满足低成本、系统可扩展性和复杂的测试环境要求。本文将探讨FPGA相关技术在汽车电子中的应用。

FPGA技术的应用领域

FPGA(Field Programmable Gate Array),是PAL、GAL、PLD等可编程器件进一步发展的产物,其逻辑功能由内部规则排列的逻辑单元阵列完成。逻辑单元阵列内部包括可配置逻辑模块、输入输出模块和内部连线

- 关键字:

汽车电子 FPGA

- 引言在电子工程设计与测试中,常常需要一些复杂的、具有特殊要求的信号,要求其波形可任意产生,频率方便可调。通常的信号产生器难以满足要求,市场上出售的任意信号产生器价格昂贵。结合实际需要,我们设计了一种任

- 关键字:

CPLD 单片机 任意波形发生器

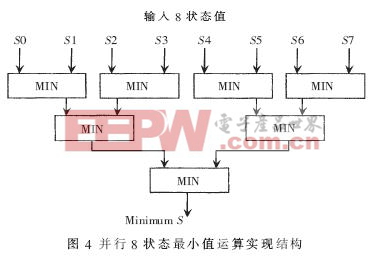

- 实现数据的高速大容量存储是数据采集系统中的一项关键技术。本设计采用Altera 公司Cyclone系列的FPGA 完成了对DDR SDRAM 的控制,以状态机来描述对DDR SDRAM 的各种时序操作,设计了DDR SDRAM 的数据与命令接口。用控

- 关键字:

SDRAM FPGA DDR 控制器

- 正文 1) 因为FPGA具有开发周期短,可更新等优点,现在有越来越多的通讯系统采用FPGA作为实际产品方案。已经有大量的FPGA应用到通讯系统中,为了降低系统维护的人力成本,需要能够实现FPGA远程版本更新。本文将以Xi

- 关键字:

FPGA 远程更新 系统

- 作为第3 代显示器,有机电致发光器件( OrganicLight Emitting Diode,OLED) 由于其主动发光、响应快、高亮度、全视角、直流低压驱动、全固态以及不易受环境影响等优异特性,具有LCD 无法比拟的优点,在手机、个人电

- 关键字:

FPGA 144C E144 OLED

- Altera公司 (NASDAQ: ALTR)日前宣布,开始提供新的Serial RapidIO® Gen2 MegaCore®功能知识产权(IP),满足全球通信基础设施系统日益增长的带宽需求。该IP新解决方案成功实现了所有硬件与最新Integrated Device Technology (IDT) RapidIO芯片的互操作性,并支持28 nm Altera Stratix® V FPGA,每通路工作速率高达6.25 Gbaud。

- 关键字:

Altera IDT 嵌入式 FPGA

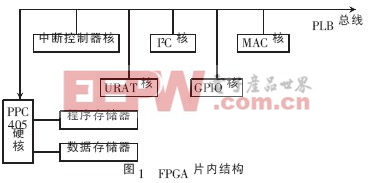

- 基于FPGA的嵌入式智能管理系统的设计与实现,近些年,针对智能管理的研究越来越广泛,采用的技术也越来越多,如基于单片机开发的智能监控平台[1]、在Linux内核下的智能仪器开发[2]、对智能管理的某一个方面进行研究[3]等。随着嵌入式核心芯片的高速发展,传统嵌

- 关键字:

设计 实现 管理系统 智能 FPGA 嵌入式 基于

- 今天,大多数的CPLD(复杂可编程逻辑器件)都采用可减少功耗的工作模式,但当系统未使用时,应完全切断电源以保存电池能量,从而实现很多设计者的终极节能目标。图1描述了如何在一片CPLD 上增加几只分立元件,实现一个

- 关键字:

CPLD 自动断电

- 1 引言ACEX 1K 系列器件是Altera 公司近期推出的新型CPLD 产品。该器件基于SRAM,结合查找表(LUT)和嵌入式阵列块(EAB)提供了高密度结构,可提供10 000 到100 000 可用门,每个嵌入式阵列块增加到16 位宽可实现双端口

- 关键字:

ACEX CPLD 配置方法

- 几年前设计专用集成电路(ASIC) 还是少数集成电路设计工程师的事, 随着硅的集成度不断提高,百万门的ASIC 已不难实现, 系统制造公司的设计人员正越来越多地采用ASIC 技术集成系统级功能(System L evel In tegrete - SL

- 关键字:

FPGA IP核 设计方法

- 高清晰度数字电视HDTV技术是当今世界上最先进的图像压缩编码技术和数字通信技术的结合。它代表一个国家的科...

- 关键字:

HDTV FPGA 译码器

- Altera公司30日宣布,在业界率先在28 nm FPGA器件上成功测试了复数高性能浮点数字信号处理(DSP)设计。独立技术分析公司Berkeley设计技术有限公司(BDTI)验证了能够在Altera Stratix® V和Arria® V 28 nm FPGA开发套件上简单方便的高效实现Altera浮点DSP设计流程,同时验证了要求较高的浮点DSP应用的性能。

Altera的浮点DSP设计流程经过规划,能够快速适应可参数赋值接口的设计更改,其工作环境包括来自MathWorks

- 关键字:

Altera FPGA DSP

- 基于FPGA的短帧Turbo译码器的实现,Turbo码虽然具有优异的译码性能,但是由于其译码复杂度高,译码延时大等问题,严重制约了Turbo码在高速通信系统中的应用。因此,如何设计一个简单有效的译码器是目前Turbo码实用化研究的重点。本文主要介绍了短帧Tur

- 关键字:

实现 Turbo FPGA 基于

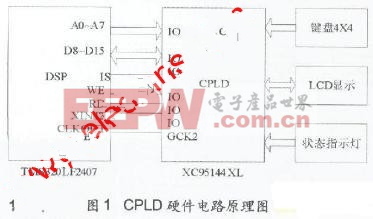

- 基于CPLD的DSP人机接口模块的设计,CPLD(Complex programmable Logic Device,复杂可编程逻辑器件)是在传统的PAL、GAL基础上发展而来的,具有多种工作方式和高集成、高速、高可靠性等明显的特点。在超高速领域和实时测控方面有非常广泛的应用,日前的C

- 关键字:

模块 设计 接口 人机 CPLD DSP 基于

cpld/fpga介绍

您好,目前还没有人创建词条cpld/fpga!

欢迎您创建该词条,阐述对cpld/fpga的理解,并与今后在此搜索cpld/fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473