- 机器对机器(M2M)系统开发可望更加快速。现今M2M产品设计人员,往往须耗费大量资源与工程周期处理基础的系统整合工作,而无暇顾及应用价值的提升,因此M2M模组厂推出更高整合度的多核心解决方案,以降低导入设计门槛。

- 关键字:

多核架构 M2M 云端管理 智能设备 Cortex-M

- 《Cortex-M3可编程片上系统原理及应用》系统化、模块化地介绍了Cypress公司的PSoC5内所集成的ARMCortex-M3CPU硬核处理器结构及指令集、PSoC5内各个功能单元的结构以及基于PSoCCreator2.0软件的片上系统的设计流程。

- 关键字:

Cortex-M3 可编程片上系统 PSoC5 PSoCCreator

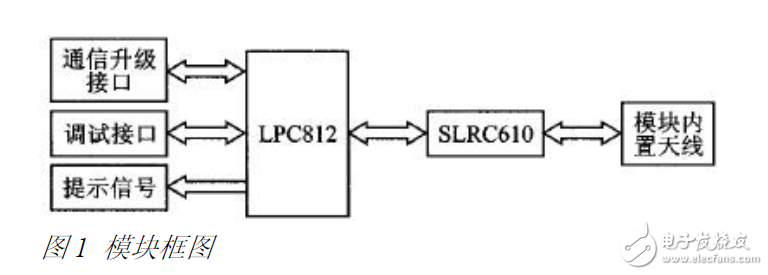

- 近年来,随着我国电网改造工作及智能电网建设的持续推进,推广智能电表已成为其中的重要内容,也是缓解电力供需矛盾、节能降耗、提高社会效益和经济效益的有效手段,电网智能化催热智能电表的大力发展。

- 关键字:

智能电表 PLC ZigBee Cortex-M0 方案

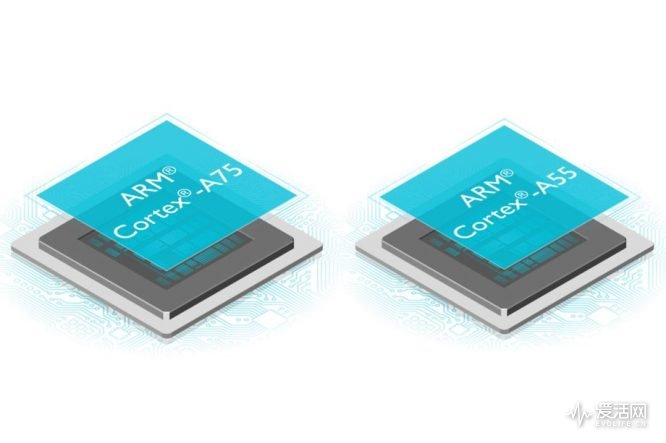

- Computex是一场PC业界的盛会,行业大佬汇聚一堂,x86平台在这场展会中唱主角,各种笔记本台式机争相斗艳,却不料ARM偏偏选择在这个节骨眼上公布Cortex-A75/A55架构,而且尽其所能地把AI、机器学习、AR/VR等流行关键词拼命往自己身上拉,似乎是要把人们的关注从以PC为主的计算领域吸引到移动计算上来。

ARM在新一代的移动计算核心里所采用的架构依旧是那套大小核做法——big.LITTLE,不过这一次它们换了个叫法:Dynamiq

- 关键字:

ARM Cortex-A75

- 2017年3月21日,ARM在北京召开新闻发布会,正式宣布推出全新的DynamlQ技术。该项技术作为未来ARM Cortex-A系列处理器的基础,代表了多核处理设计行业的转折点,其灵活多样性将重新定义更多类别设备的多核体验,覆盖从端到云的安全、通用平台。DynamlQ技术将被广泛应用于汽车、家庭以及数不胜数的各种互联设备,以实现更先进的人工智能。

- 关键字:

ARM Cortex-A

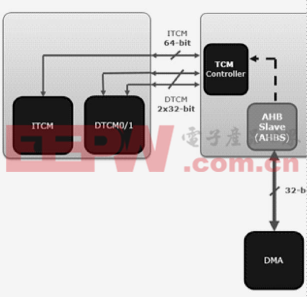

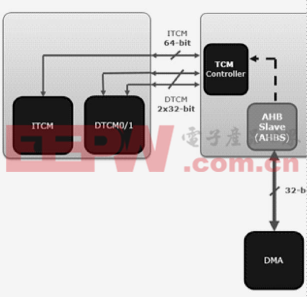

- 对于那些需要低功耗、成本效益和中等性能的嵌入式系统而言,ARM Cortex M系列无疑是首选的处理器系列。 Cortex M系列中最早得到应用的是其光谱中的小部分产品: Cortex M0用于实现最低的成本,Cortex M0+用于实现最高 的能效,Cortex M3用于实现功耗与性能之间的最佳平衡, Cortex M4用于实现那些需要数字信号处理(DSP)功能的应 用。 该系列中最高性能的Cortex M7的首批应用现已开

- 关键字:

Cortex M7 内存

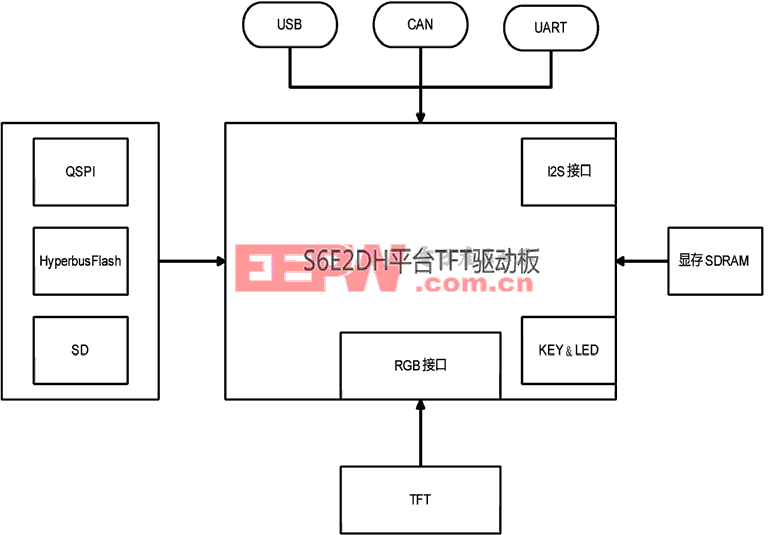

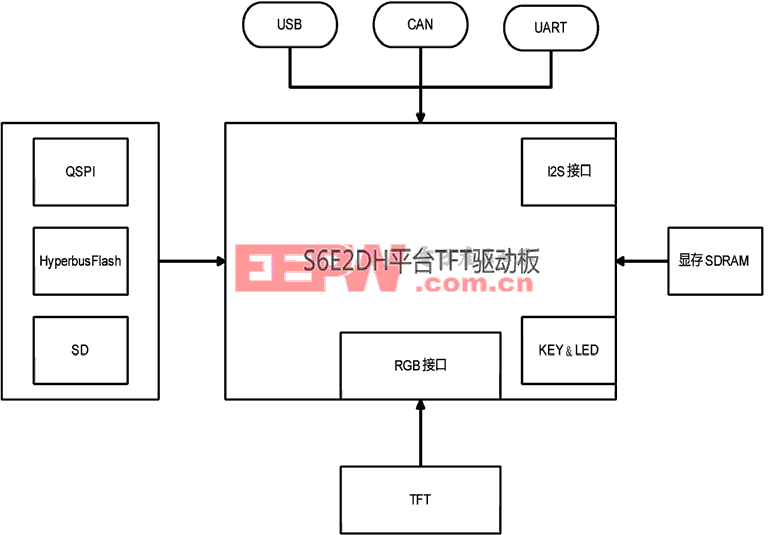

- 引言 目前在物联网相关应用中,包括使能家具显示面板、 工控显示面板、手持设备、人脸识别等领域都在逐步由传统 的黑白点阵LCD或者段式LCD显示向彩色TFT屏显示发展, 主要是因为彩色TFT屏幕显示内容丰富而且价格也越来越便 宜,但是基于彩色TFT的显示面板大都显示内容复 杂,效果多,素材占用资源大,这就对微处理器的 处理能力提出了更高的要求,现在大多数的方案都 是基于ARM9、A8或者更高端的处理器去实现相关 功能,这些方案实现起来开发复杂,开发周期长, BOM成本

- 关键字:

Cypress Cortex-M4 显示

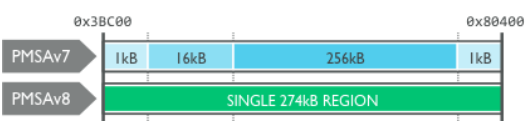

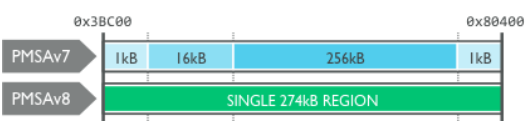

- ARM® Cortex®-M23采用TrustZone®技术,是尺寸最小、能效最高的处理器。小型嵌入式应用对芯片的安全性能有严格要求,基于ARMv8-M基线架构的Cortex-M23处理器则是最佳解决方案。 本文中,我将带各位领略全新Cortex-M23处理器的强大特色: Cortex-M23最重要的特色是加入了TrustZone安全基础技术 极紧凑的架构与布线 强化的调试纠错和追溯能力(对开发商的生产力提高至关重要) 存储保护单元获得改善(该单元定义软件组件的访问许可,全新设计提

- 关键字:

ARM Cortex-M23

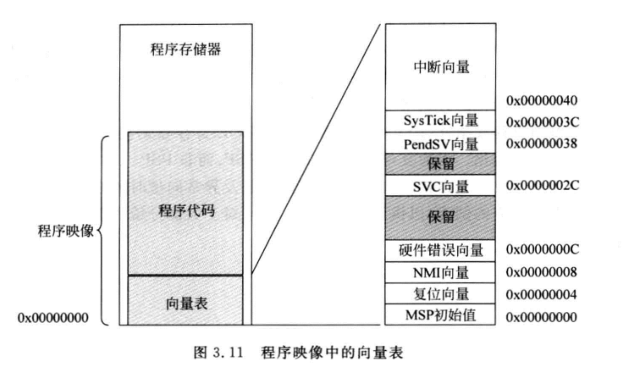

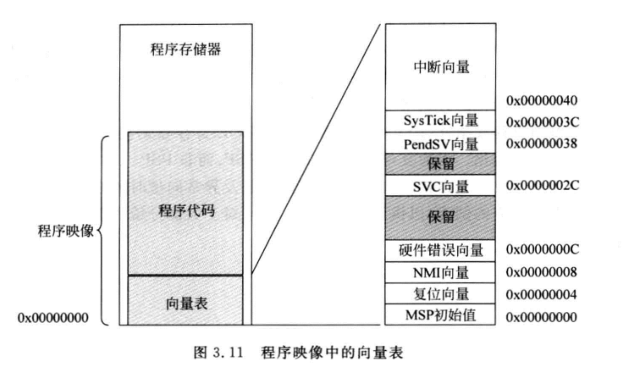

- 我们先来看看程序映像。

通常,Cortex-M0处理器的程序映像时从地址0x00000000处开始的。 程序映像开始处时向量表,其中包含了异常的其实地址(向量),每个中断向量的地址都等于“异常号*4”,比如,外部IRQ0的异常类型为16,因此其向量地址为16*4=0x40。这些向量的最低位都被置为1,以表示使用thumb指令。向量表的大小由实际使用的中断个数决定。 向量表中包含了MSP的初始值,它存储在向量表的头四个字节。 复位时,处理器首先读取向量

- 关键字:

Cortex-M0 处理器

- 基于ARM Cortex处理器的片上系统(SoC)解决方案适用于多种嵌入式设计细分市场,如物联网、电机控制、医疗、汽车、家电自动化等。我们的处理器品种丰富且基于同一个标准架构,针对不同的产品市场提供广泛而丰富的性能与成本组合。

Cortex系列处理器主要基于3大产品类型量身开发,A系列:运行复杂系统的精细高端应用;R系列:高性能硬实时系统;M系列:低功耗、确定性、成本敏感的微控制器,专门优化以满足其需求。

最先采用ARMv8-M架构的2款处理器为Cortex-M23和Cortex-M33。

- 关键字:

ARM Cortex-M33

- 为了管理中断请求的优先级并处理其他异常,Cortex-M0处理器内置了嵌套中断控制器(NVIC)。NVIC的一些可编程控制器控制着中断管理功能,这些寄存器被映射到系统地址空间里,它们所处的区域被称为系统控制空间(SCS)。

NVIC有以下特性: 灵活的中断管理; 支持嵌套中断; 向量化的异常入口 中断屏蔽 灵活的中断管理 Cortex-M0处理器中,每一个外部中断都可以被使能或者禁止,并且可以被设置为挂起状态或者清除状态。处理器的中断可以是信号

- 关键字:

Cortex-M0 中断

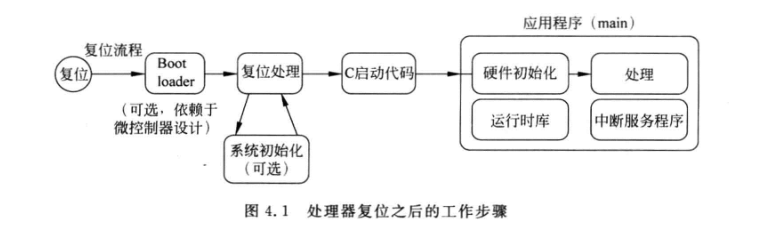

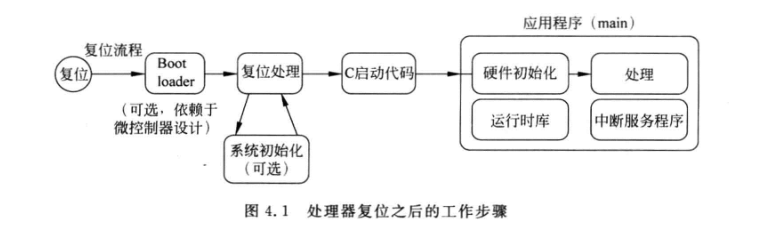

- 嵌入式系统编程入门 微控制器是如何启动的 为了保存编译号的二进制程序代码,大多数的现代微控制器都会包含片上flash存储器。有些微控制器还可能有一个独立的启动ROM,里面装有Bootloader程序。微控制器启动后,再执行flash的用户程序前,Bootloader会首先运行。 在复位流程中,处理器会取出MSP的初始化值和复位向量,然后开始执行复位处理,这些信息都放在一个叫做启动代码的程序文件中。启动代码中的复位处理可能还会旅行初始化的职责,比如时钟控制电路和锁相环PLL的初始化。有些情况下,系

- 关键字:

Cortex-M0

- 异常会引起程序控制的变化。在异常发生时,处理器停止当前的任务,转而执行异常处理程序,异常处理完成后,会继续执行刚才的任务。异常分为很多种,中断是其中之一。Cortex-M0处理器最多支持32个外部中断(IRQ)和一个不可屏蔽中断(NMI),中断事件的处理叫做中断服务程序(ISR),中断一般由片上的IO口的外部输入产生(边沿触发和电平触发)。 Cortex-M0处理器上可用的中断数量不确定,由厂商决定,最多32个外部中断。如果系统的外设很多,由于中断数目有限,多个中断源可能使用同一个中断连接。 除了

- 关键字:

Cortex-M0 中断

- 为了管理中断请求的优先级并处理其他异常,Cortex-M0处理器内置了嵌套中断控制器(NVIC)。NVIC的一些可编程控制器控制着中断管理功能,这些寄存器被映射到系统地址空间里,它们所处的区域被称为系统控制空间(SCS)。 NVIC有以下特性: 灵活的中断管理; 支持嵌套中断; 向量化的异常入口 中断屏蔽 灵活的中断管理 Cortex-M0处理器中,每一个外部中断都可以被使能或者禁止,并且可以被设置为挂起状态或者清除状态。处理器的中断可以是信号级的(在中断服务程序清除中断请求以前,外设的

- 关键字:

Cortex-M0 NVIC

- 岁末年终,一波波购物海潮澎湃来袭,圣诞季与新年季也正式拉开了帷幕。给晚辈,给爱人,给孩子的过节礼品你都预备好了吗?这一次,让ARM来为你推荐几款新鲜新颖的小玩艺儿吧,相信一定会陪同你珍爱的人渡过异乎寻常的假期。 【Hush智能耳塞:睡得平稳,起得准时】 歇息和节日老是一对形影不离的好朋友,繁忙了一年,总算可以趁着节日的空档好好补个觉。快来尝尝Hush吧!它可是号称“世界上第一款智能耳塞”呢。Hush拙劣地将热迟钝回忆泡沫耳塞和播放舒缓音效的耳机相结合,无效地将乐音和搅扰阻隔在好梦外。固然,用户也不

- 关键字:

ARM Cortex-M4

cortex—m3介绍

您好,目前还没有人创建词条cortex—m3!

欢迎您创建该词条,阐述对cortex—m3的理解,并与今后在此搜索cortex—m3的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473