- 导读:ACD又称模数转换器,是将模拟连续变化信号变换为数字离散信号的新型电子元件。小编带大家了解ADC的原理,究其竟是如何将模拟信号转变为数字信号的。

ADC原理——什么是ADC

将模拟信号转换成数字信号的电路,称为模数转换器(简称ADC),A/D转换的作用是将时间连续、幅值也连续的模拟量转换为时间离散、幅值也离散的数字信号,因此,A/D转换一般要经过取样、保持、量化及编码4个过程。在实际电路中,这些过程有的是合并进行的,例如,取样和保持,量化和编码往往都是在转换过

- 关键字:

ADC ADC原理

- 运算放大器是作为最通用的模拟器件,广泛用于信号变换调理、ADC采样前端、电源电路等场合中。虽然运放外围电路简单,不过在使用过程中还是有很多需要注意的地方。

1、注意输入电压是否超限

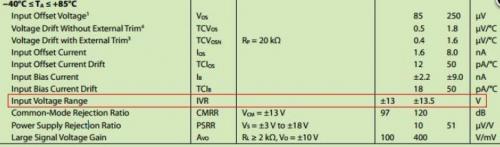

图1是ADI的OP07数据表中的输入电气特性的一部分,可以看到在电源电压±15V的条件下,输入电压的范围是±13.5V,如果输入电压超出范围,那么运放就会工作不正常,出现一些意料不到的情况。

而有一些运放标注的不是输入电压范围,而是共模输入电压范围,如图1-2是TI的TLC22

- 关键字:

运算放大器 ADC

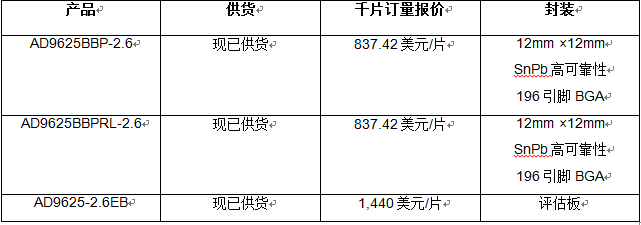

- Analog Devices, Inc.近日宣布针对航空航天和国防应用中的高带宽和动态范围要求推出2.6 GHz ADC AD9625BBP-2.6。AD9625BBP-2.6 12位ADC兼具GHz采样速率和75 dBc无杂散动态范围(SFDR)性能,支持1.8 GHz Ain,完全针对满足高级电子监控和反监控应用中的频率规划和信号灵敏度要求而优化,如雷达系统、安全通信网络和电子信号监控应用。这款新型转换器提供锡铅(SnPb)封装,通过采用替代封装材料解决了易受锡须影响而导致性能下降和成本上升的问题

- 关键字:

ADI ADC

- 日前,德州仪器 (TI) 宣布推出业界首款16位1 GSPS模数转换器 (ADC) ADS54J60,这也是业内首例在1 GSPS 采样速率下实现超过70 dBFS信噪比 (SNR) 的模数转换器。另外,TI 还推出了最高密度的四通道14位500 MSPS 数转换器——ADS54J54。为了优化信号链,TI 的新型LMH6401 4.5 GHz全差分数字可变增益放大器 (DVGA) 提供了最宽的带宽和DC耦合,并实现了低频和高频信号采集,此外,还不受 AC 耦合型系统

- 关键字:

TI ADC

- 输入共模电压范围(Vcm)对于包含了基带采样和高速ADC的通信接收机设计非常重要,尤其是采用直流耦合输入、单电源供电的低压电路。对于单电源供电电路,馈送到放大器和ADC的输入信号应该偏置在Vcm范围以内的直流电平,能够消除放大器和ADC设计的一大屏障,因为不必在0V保持低失真和高线性度。

直接下变频结构的无线通信接收机通常采用差分、直流耦合方式与ADC连接。这种电路包含一个零中频(ZIF)结构,具有一个RF正交解调器和双通道基带ADC。ZIF电路省去了多级IF下变频器和SAW滤波器,因而受到了普

- 关键字:

ADC MAX1185

- 1 AD9225的结构

AD9225是ADI公司生产的单片、单电源供电、12位精度、25Msps高速模数转换器,片内集成高性能的采样保持放大器和参考电压源。AD9225采用带有误差校正逻辑的四级差分流水结构,以保证在25Msps采样率下获得精确的12位数据。除了最后一级,每一级都有一个低分辨率的闪速A/D与一个残差放大器(MDAC)相连。此放大器用来放大重建DAC的输出和下一级闪速A/D的输入差,每一级的最后一位作为冗余位,以校验数字误差,其结构如图1所示。

图

- 关键字:

ADC FIFO

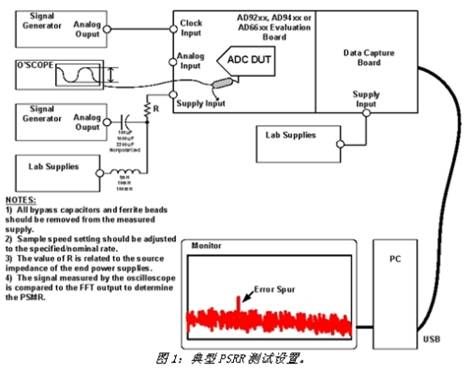

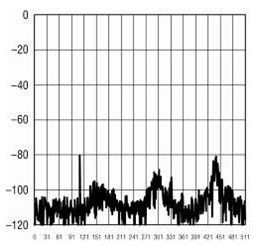

- 当今许多应用要求高速采样模数转换器(ADC)具有12位或以上的分辨率,以便用户能够进行更精确的系统测量。遗憾的是,更高的分辨率也意味着系统对噪声更加敏感。系统分辨率每提高一位,例如从12位提高到13位,系统对噪声的敏感度就会提高一倍。因此,对于ADC设计,设计人员必须考虑一个常常被遗忘的噪声源——系统电源。ADC是敏感器件,为了实现数据手册所述的最佳额定性能,应当同等看待模拟、时钟和电源等所有输入端。噪声来源众多,形式多样,噪声辐射会影响性能。

当今电子业界的时髦概念是新

- 关键字:

ADC PSRR

- 正确选择输入网络元件对于高速ADC的驱动和输入网络的平衡至关重要(参考应用笔记:“正确选择输入网络,优化高速ADC的动态性能和增益平坦度”)。

在较高IF应用中,端接电阻的位置非常重要。交流耦合输入信号可以在变压器的原边或副边端接,具体取决于系统对高速ADC增益平坦度和动态范围的要求。宽带变压器是一个常用元件,能够在较宽的频率范围内将单端信号转换成差分信号,提供了一种快速、便捷的解决方案。

原边端接

本文以MAX1124 (Maxim近期推出的250MHz、1

- 关键字:

ADC 变压器

- 消除模数转换链路中的数字反馈可能是一个挑战。在把数字输出与模拟信号链路及编码时钟隔离开来的板级设计过程中,即使在极为谨慎的情况下,模数转换器 (ADC) 输出频谱中也有可能观察到某些数字反馈的现象,从而导致转换器动态范围性能的下降。尽管良好的布局可以帮助减轻耦合回模拟输入的数字噪声的影响,但是这种办法也许不足以消除数字反馈这个问题。本文解释了数字反馈,并讨论了一种新的创新性 ADC,这种 ADC 内置了一些功能,在良好设计的布局也许不足以解决问题的情况下,这些功能可用来克服数字反馈。

数字反馈

- 关键字:

ADC 数字反馈

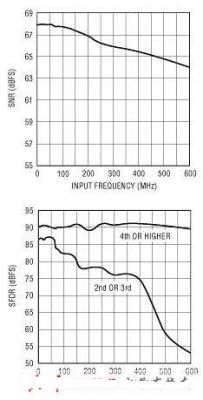

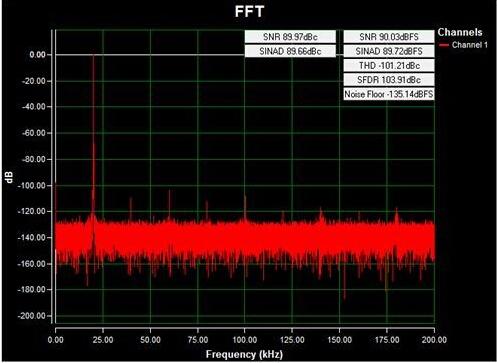

- 包含千兆采样率ADC的系统设计会遇到许多复杂情况。面临的主要挑战包括时钟驱动、模拟输入级和高速数字接口。本文探讨了如何才能克服这些挑战,并给出了在千兆赫兹的速度下进行系统优化的方法。在讨论中,时钟设计、差分输入驱动器的设计、数字接口和布局考虑都是十分复杂的问题。本文中的参考设计将采用ADC083000/B3000。

时钟源是高速数据转换系统中最重要的子电路之一。这是因为时钟信号的定时精度会直接影响ADC的动态性能。为了将这种影响最小化,ADC的时钟源必须 具有很低的定时抖动或相位噪声。如果在选择

- 关键字:

ADC ADC083000

- 高速ADC的性能特性对整个信号处理链路的设计影响巨大。系统设计师在考虑ADC对基带影响的同时,还必须考虑对射频(RF)和数字电路系统的影响。由于ADC位于模拟和数字区域之间,评价和选择的责任常常落在系统设计师身上,而系统设计师并不都是ADC专家。

还有一些重要因素用户在最初选择高性能ADC时常常忽视。他们可能要等到最初设计样机将要完成时才能知道所有系统级结果,而此时已不太可能再选择另外的ADC。

影响很多无线通信系统的重要因素之一就是低输入信号电平时的失真度。大多数无线传输到达ADC的信号

- 关键字:

ADC CMOS

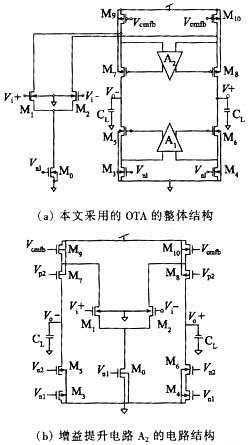

- 近年来,随着数字信号处理技术的迅猛发展,数字信号处理技术广泛地应用于各个领域。因此对作为模拟和数字系统之间桥梁的模数转换器(ADC)的性能也提出了越来越高的要求。低电压高速ADC在许多的电子器件的应用中是一个关键部分。由于其他结构诸如两步快闪结构或内插式结构都很难在高输入频率下提供低谐波失真,因此流水线结构在高速低功耗的ADC应用中也成为一个比较常用的结构。

作为流水线ADC前端的采样保持电路是整个系统的关键模块电路之一。设计一个性能优异的采样保持电路是避免采样歪斜(timing skew)最直

- 关键字:

ADC 采样保持

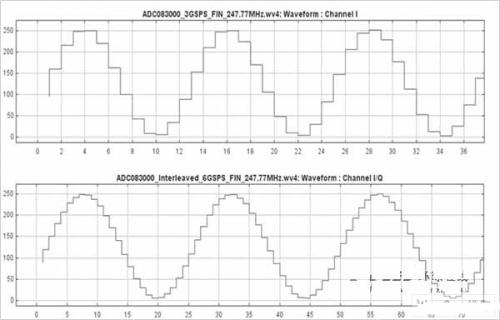

- 运用时序交错式类比数位转换器(timeinterleavedADC)在每秒高达数十亿次的同步取样类比讯号是一个技术上的挑战,除此之外,对於混合讯号电路的设计也需要非常谨慎小心。基本上,时序交错的目标是利用转换器数目与取样频率相乘而不影响解析度以及动态的效能。

本文将探讨运用时序交错式类比数位转换器时所出现的技术挑战,并对此提供实用的系统设计解决方案。本文也将说明可以解决目前已知问题的创新元件的特色及设计技术。同时利用快速傅立叶转换(FFT)计算法算出7GSPS速率及两个转换器晶片在「交错解决方案

- 关键字:

PCB ADC

- 引言

在当今工业自动化应用中,复杂的控制系统代替人工来操作不同的机器和过程。术语“自动化”指其智能化足以制定正确的过程决策从而实现目标结果的系统。我们这里所说的“系统”是指闭环控制系统。这些系统依赖于输入至控制器的传感器数据,提供反馈,控制器据此采取措施。这些措施就是控制器输出的变化。通过确保高性能、高可靠性工业操作,闭环控制系统对于现代化工业4.0工厂的工业自动化和效率至关重要。

本文讨论闭环系统的关键要素,重点关注模/数转换器(ADC)和

- 关键字:

ADC DAC

- 一些工程师在设计过程中经常会发出疑问“为什么ADC的额定最小和最大增益误差相差如此之大?”在此将针对该问题进行深入探讨并给予解答。

为特定应用选择高速ADC时,增益一般不是关键规格。在设计阶段会更重视噪声、失真、功耗和价格。但这些年来,我们了解到,一旦ADC和信号链中的所有其他器件得以明确,某些幸运的工程师会计算复合信号链的增益,判断它会如何影响系统。ADC通常不是总偏差的主要贡献者,但某些器件要比其他器件更糟糕。

增益误差指实测满量程与理想满量程之差,通常用满量程

- 关键字:

ADI ADC

adc介绍

英文缩写: ADC (Analog to Digital Converter)

中文译名: 模数变换器

分 类: IP与多媒体

解 释: 将连续变量的模拟信号转换为离散的数字信号的器件。 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473