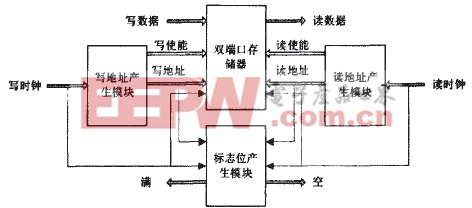

- 高速异步FIFO的设计与实现,引言 现代集成电路芯片中,随着设计规模的不断扩大.一个系统中往往含有数个时钟。多时钟带来的一个问题就是,如何设计异步时钟之间的接口电路。异步FIFO(First In First Out)是解决这个问题的一种简便、快捷的解

- 关键字:

实现 设计 FIFO 异步 高速

- 摘要:高性能ADC采集系统前端电路的设计及ADC本身固有的特点对系统性能的影响至关重要,优化高速采样系统设计取决于很多因素,包括应用性质、系统组成和ADC的结构,本文主要介绍了使用放大器或变压器作为ADC前端电路

- 关键字:

考虑 分析 电路设计 系统 ADC 采集 高速

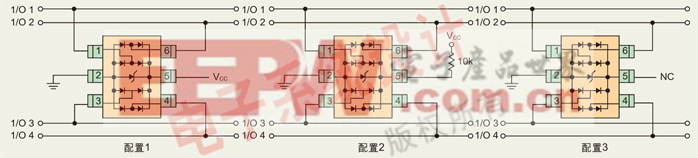

- USB 2.0高速端口的ESD保护设计方案,通用串行总线(USB)高速数据应用也十分普遍,用户在热插拨任何USB外设时可能会导致ESD事件。此外,在离导电表面几英寸的地方也可能发生空气放电,可能损坏USB接口及芯片。因此,设计人员必须为USB元件提供ESD保护。 业

- 关键字:

设计 方案 保护 ESD 2.0 高速 USB

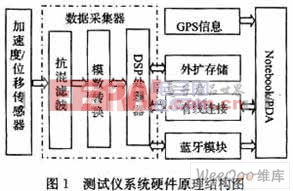

- 基于DSP的高速列车测振仪,0 引 言

列车的振动性能,包括舒适性、平稳性的检测与*价是新型列车研究、检验过程中的一项重要工作。随着我国铁路新型高速列车研究、研制及实验运行工作的大面积展开,十分需要一种方便、快捷的便携式列车振动测试

- 关键字:

列车 高速 DSP 基于

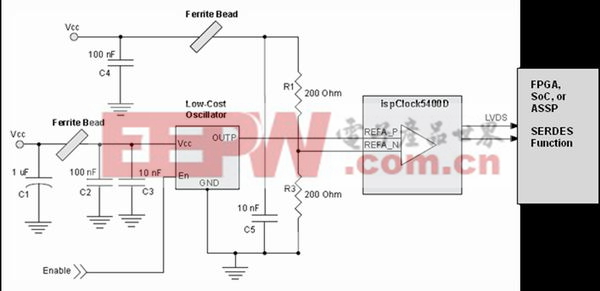

- 高速串行接口设计的高效时钟解决方案,数字系统的设计师们面临着许多新的挑战,例如使用采用了串行器/解串器(SERDES)技术的高速串行接口来取代传统的并行总线架构。基于SERDES的设计增加了带宽,减少了信号数量,同时带来了诸如减少布线冲突、降低开关噪

- 关键字:

时钟 解决方案 高效 设计 串行 接口 高速

- 高速DSP串行外设接口设计, 1 引言DSP(数字信号处理)的优势除了处理复杂的运算,特别适用于数字滤波、语音、视频、图象处理、通信以及高速实时测控系统中已成为现代信息处理技术的重要器件,极大地促进了信号处理和测控各个领域的学术研究、产

- 关键字:

接口 设计 外设 串行 DSP 高速 DSP

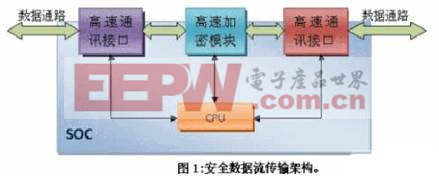

- SOC的高速数据流加密传输的方法实现,计算机技术的发展使移动存储设备代替纸张逐渐成为信息传递的主要方式,无纸化办公也逐渐成为行业用户的主要办公方式。随着电子商务、数字管理以及移动办公等现代行业的迅猛发展,行业用户(政府、企业、*、涉密机关)对

- 关键字:

方法 实现 传输 加密 高速 数据流 SOC

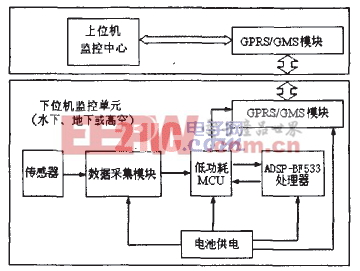

- ADSP-BF533在低耗高速实时系统中的应用,本文提出了一种基于单片机+ADSP BF533的双核结构,适用于一些具有低功耗、高速实时处理特点的系统。利用这种双核结构,可以兼顾高速实时数据处理和节约能源的要求,可在许多相关领域发挥无与伦比的作用。

- 关键字:

系统 应用 实时 高速 低耗 ADSP-BF533 数字信号

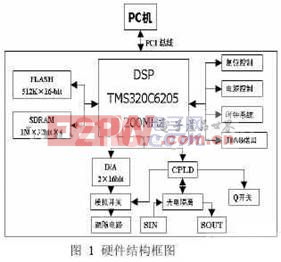

- 基于DSP的高速激光标记控制系统设计, 0 引言 振镜扫描式激光标记技术就是通过控制两片高速振镜的偏转角, 改变激光的传播方向, 经过F-Theata透镜在工件表面的聚焦, 在工件表面作标记。与传统的标记技术相比, 它具有适用面广(对不同材料、形状的加工表

- 关键字:

控制系统 设计 标记 激光 DSP 高速 基于

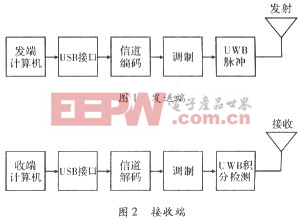

- 摘要: 采用高速USB接口连接计算机终端与UWB通信系统基带模块,设计并实现了USB接口电路,控制UWB通信系统基带模块与USB接口设备的数据传输,最终实现了终端电脑与UWB通信系统的数据传输。实际测试中,USB接口的速率约

- 关键字:

接口 设计 实现 USB 高速 通信 系统 IR-UWB

- FPGA高速收发器设计原则,高速收发器(SERDES)的运用范围十分广泛, 包括通讯、计算机、工业和储存,以及必须在芯片与芯片/模块之间、或在背板/电缆上传输大量数据的系统。但普通高速收发器的并行总线设计已无法满足现在的要求。将收发器整合在FPGA中,成为解决这一问题的选择办法。

- 关键字:

原则 设计 收发器 高速 FPGA RapidIO

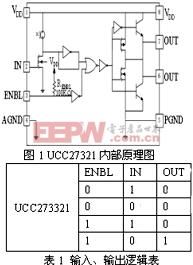

- 基于UCC27321高速MOSFET驱动芯片的功能与应用,1 引言

随着电力电子技术的发展,各种新型的驱动芯片层出不穷,为驱动电路的设计提供了更多的选择和设计思路,外围电路大大减少,使得MOSFET的驱动电路愈来愈简洁,.性能也获得到了很大地提高。其中UCC27321

- 关键字:

芯片 功能 应用 驱动 MOSFET UCC27321 高速 基于

- 1.引言随着电子产品功能的日益复杂和性能的提高,印刷电路板的密度和其相关器件的频率都不断攀升,保持并提高系统的速度与性能成为设计者面前的一个重要课题。信号频率变高,边沿变陡,印刷电路板的尺寸变小,布线密

- 关键字:

最小化 及其 分析 PCB 高速 耦合

- 由于系统时钟频率和上升时间的增长,信号完整性设计变得越来越重要。不幸的是,绝大多数数字电路设计者并没意识到信号完整性问题的重要性,或者是直到设计的最后阶段才初步认识到。 本篇介绍了高速数字硬件电路设

- 关键字:

分析 完整性 信号 电路设计 高速

- 低电压差分信号(LVDS)非常适合时钟分配、一点到多点之间的信号传输。本文描述了使用LVDS将高速信号分配到多个目的端的方法。 在一个数字系统中,当各个子系统需要相同的参考时钟源协同工作时,时钟分配非常重要

- 关键字:

信号 传输 高速 LVDS 通过 差分 电压

高速介绍

您好,目前还没有人创建词条高速!

欢迎您创建该词条,阐述对高速的理解,并与今后在此搜索高速的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473