- 入门

结合一两个小项目把上面所说的事情都做好后,差不多就可以进入入门的阶段了(要求稍微严格了一点点,呵呵)。

入门阶段要学的有:设计时序;理解约束的原理及如何加约束。

先谈谈设计时序。

设计时序是进行逻辑设计的基本要求:时序是设计出来的,不是仿出来的,更不是凑出来的。

很多人在做逻辑设计时喜欢一上来就狂写代码,写到一半后发现信号间的时序出问题了,只好推倒重来;好不容易反复了几次之后,通过仿真软件看了下,差不多要对了,于是再凑一下时序,竟然对了!但这个做法除了设计周期长外,

- 关键字:

逻辑设计 时序 约束

- 当你的FPGA设计不能满足时序要求时,原因也许并不明显。解决方案不仅仅依赖于使用FPGA的实现工具来优化设计从而满足时序要求,也需要设计者具有明确目标和诊断/隔离时序问题的能力。设计者现在有一些小技巧和帮助来设置时钟;使用像Synopsys Synplify Premier一样的工具正确地设置时序约束;然后调整参数使之满足赛灵思FPGA设计性能的目标。

会有来自不同角度的挑战,包括:

● 更好的设计计划,例如完整的和精确的时序约束和时钟规范

● 节约时间的设计技术,例如为更好的性能结

- 关键字:

FPGA Synplify 时序

- 在网络通讯领域,ATM交换机、核心路由器、千兆以太网以及各种网关设备中,系统数据速率、时钟速率不断提高,相应处理器的工作频率也越来越高;数据、语音、图像的传输速度已经远远高于500Mbps,数百兆乃至数吉的背板也越来越普遍。数字系统速度的提高意味着信号的升降时间尽可能短,由数字信号频率和边沿速率提高而产生的一系列高速设计问题也变得越来越突出。当信号的互连延迟大于边沿信号翻转时间的20%时,板上的信号导线就会呈现出传输线效应,这样的设计就成为高速设计。高速问题的出现给硬件设计带来了更大的挑战,有许多从逻

- 关键字:

PCB 时钟 时序

- 规范很重要

工作过的朋友肯定知道,公司里是很强调规范的,特别是对于大的设计(无论软件还是硬件),不按照规范走几乎是不可实现的。逻辑设计也是这样:如果不按规范做的话,过一个月后调试时发现有错,回头再看自己写的代码,估计很多信号功能都忘了,更不要说检错了;如果一个项目做了一半一个人走了,接班的估计得从头开始设计;如果需要在原来的版本基础上增加新功能,很可能也得从头来过,很难做到设计的可重用性。

在逻辑方面,我觉得比较重要的规范有这些:

1.设计必须文档化。要将设计思路,详细实现等写入文档

- 关键字:

FPGA 时序 电路

- 时序的由来我们已经知道单片机执行指令的过程就是顺序地从ROM程序存储器中取出指令一条一条的顺序执行然后 ...

- 关键字:

单片机 时序 周期

- 51单片机时序及延时分析计算机工作时,是在统一的时钟脉冲控制下一拍一拍地进行的。这个脉冲是由单片机控制 ...

- 关键字:

51单片机 时序 延时分析

- 由于工程师们都在竭尽所能地获得其电源的最高效率,时序优化正变得越来越重要。在开关期间,存在两个过渡阶段:低...

- 关键字:

电源设计 同步降压 FET 时序

- 由于火箭炮发射的是简易控制火箭弹,因此其定向管与火箭弹之间的电气信号接口除了与普通无控火箭弹一样具有点火信号接口外,还另有一个32芯参数装定信号接口。在发射程序中,如果火控系统计算的火箭弹的飞行控制参数

- 关键字:

检测系统 设计 时序 单片机 MSP430F149 基于

- 摘要:设计了一种用于OTP存储器的片上时序信号产生电路。由地址变化探测电路和脉冲宽度调整电路组成。地址变化检测电路检测地址信号的变化,再由脉冲宽度调整电路产生一个宽度适中的时序信号,用于内部时序控制。其具

- 关键字:

OTP 存储器 时序 信号产生电路

- 如何有效的管理FPGA设计中的时序问题, 当

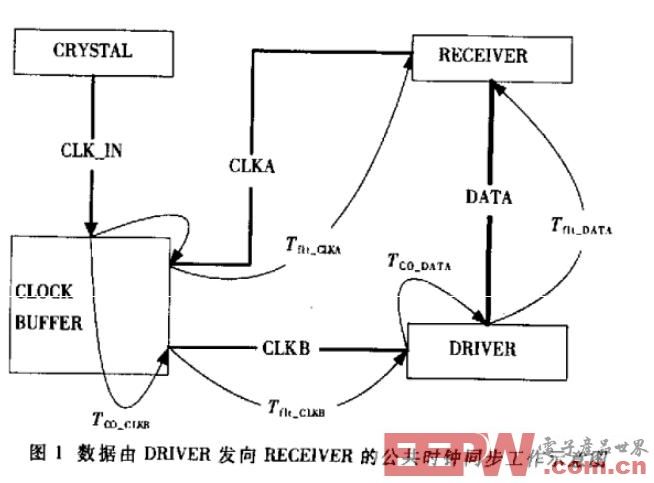

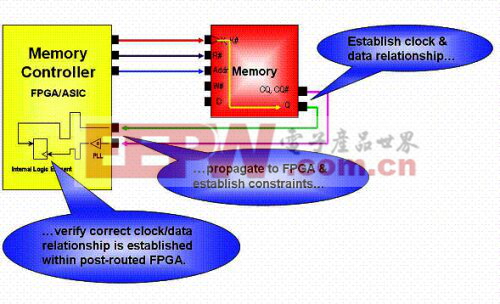

二、导言 FPGA的设计与高速接口技术可以帮助你满足今天的市场要求,但也提出了一些有趣的设计挑战。为了确保存储器接口的数据传输准确,在超过200兆赫兹以上,进行时序分析将发挥更突出的作用,以

- 关键字:

时序 问题 设计 FPGA 有效 管理 如何

- FPGA时序收敛分析,您编写的代码是不是虽然在仿真器中表现正常,但是在现场却断断续续出错?要不然就是有可能在您使用更高版本的工具链进行编译时,它开始出错。您检查自己的测试平台,并确认测试已经做到 100% 的完全覆盖,而且所有测试

- 关键字:

分析 收敛 时序 FPGA

- 单片机内部的时序

单片机执行各种操作时,CPU都是严格按照规定的时间顺序完成相关的工作,这种时间上的先后顺序成为时序。

单周期指令的操作时序

双周期指令的操作时序

时钟电路

时钟电路参数:

频

- 关键字:

分析 时序 内部 单片机

- 单片机内部的时序 单片机执行各种操作时,CPU都是严格按照规定的时间顺序完成相关的工作,这种时间上的先后顺序成为时序。

单周期指令的操作时序

双周期指令的操作时序

时钟电路

时钟电路参数:

频率

- 关键字:

简介 时序 内部 单片机

- 为了避免同步RS触发器的输入信号同时为1,可以在S和R之间接一个“非门”,信号只从S端输入,并将S端改称为数据输入端D,如图15-8所示。这种单输入的触发器称为同步D触发器,也称D锁存器。

由图可知,S=D,

- 关键字:

D触发器 时序 原理

- SOC时序分析中的跳变点介绍, 跳变点是所有重要时序分析工具中的一个重要概念。跳变点被时序分析工具用来计算设计节点上的时延与过渡值。跳变点的有些不同含义可能会被时序分析工程师忽略。而这在SOC设计后期,也就是要对时序签字时可能会导致问

- 关键字:

介绍 分析 时序 SOC

时序介绍

您好,目前还没有人创建词条时序!

欢迎您创建该词条,阐述对时序的理解,并与今后在此搜索时序的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473