- 在现阶段数字电路的设计过程中,通过 EDA 技术的应用可以改变传统的数字电路的运营模式,对错误的程序性模式可以做出及时的修改。因此,本文通过对现阶

- 关键字:

数字电路 EDA 技术应用

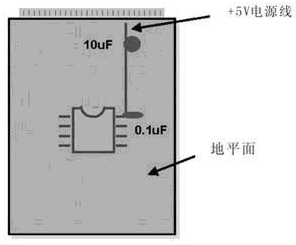

- 印制电路板设计是电子产品制作的重要环节,其合理与否不仅关系到电路在装配、焊 接、调试和检修过程中是否方便,而且直接影响到产品的质量与电气性能,

- 关键字:

数字电路 电源

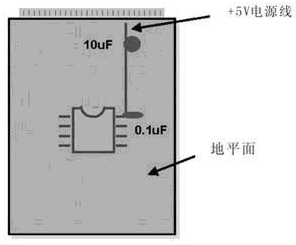

- 本文就旁路电容、电源、地线设计、电压误差和由PCB布线引起的电磁干扰(EMI)等几个方面,讨论模拟和数字布线的基本相似之处及差别。 工程领域中的数字设计人员和数字电路板设计专家在不断增加,这反映了行业的发展趋势。尽管对数字设计的重视带来了电子产品的重大发展,但仍然存在,而且还会一直存在一部分与模拟或现实环境接口的电路设计。模拟和数字领域的布线策略有一些类似之处,但要获得更好的结果时,由于其布线策略不同,简单电路布线设计就不再是最优方案了。本文就旁路电容、电源、地线设计、电压误差和由PCB布线引起的电

- 关键字:

PCB 数字电路

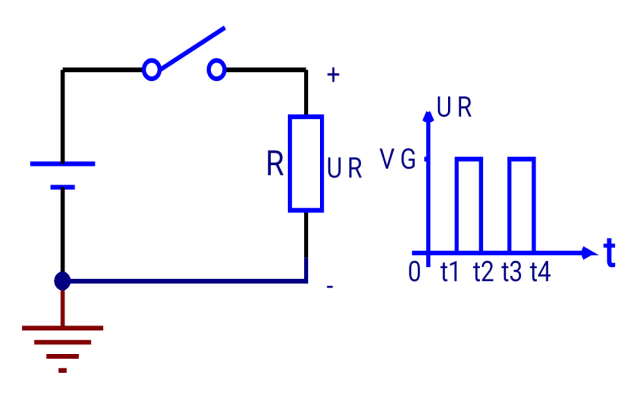

- 事实上,它是由常用的电路结构所决定的,低电平时电路往往有较高电平时更低的环路阻抗,而低阻抗则意味着抗干扰能力更强。结合实际讲一个有用的例子来加深印象: 我们有的同学可能已经学习了这样的一条PCB布线规则-----在条件许可的情况下,高电平有效线要尽量缩短,低电平有效的线则尽量延长----这一条规则的存在基础就是基于低电平时环路阻抗比较低,抗干扰能力比较强才起来的。 如OC或OD电路要控制一个电平就是通过它这个开关的通断来实现的。有在上拉电阻的情况下,开关接通,得低电平;开关切断,得高电平。这样,为

- 关键字:

数字电路 低电平

- 这是一个在逻辑设计中注意事项列表,由此引起的错误常使得设计不可靠或速度较慢,为了提高设计性能和提高速度的可靠性,必须确定设计通过所有的这些检查。 可靠性 1. 为时钟信号选用全局时钟缓冲器BUFG! 不选用全局时钟缓冲器的时钟将会引入偏差。 2. 只用一个时钟沿来寄存数据 使用时钟的两个沿是不可靠的,因为时钟的某沿或者两个沿会漂移。如果时钟有漂移而且你只使用了时钟的一个沿,你就降低了时钟边沿漂移的风险。这个问题可以这样来解决:就是允许CLKDLL自动纠正时钟的占空比,以达

- 关键字:

数字电路

- 数字电路之数字集成电路IC-在上一期《数字电路之如雷贯耳的“逻辑电路”》中我们了解了基本的逻辑电路,本期将讲解数字IC的基础和组合电路。

- 关键字:

数字电路 逻辑IC COMS TTL

- 数字电路之如雷贯耳的“逻辑电路”-本文我们将从“数字意味着什么?”开始,讲解数字电路的基本设计方法。什么是“模拟”和“数字”。在自然界中,象声音、温度、光等信息是以连续的值进行变化的。这种连续值就称作“模拟”。

- 关键字:

数字电路 逻辑电路 模拟电路

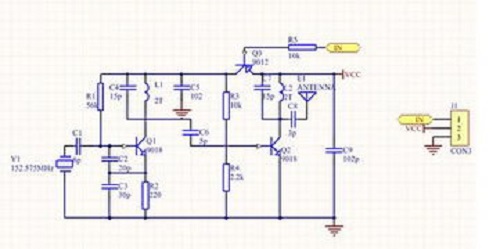

- 相近又有所区别,解析射频和数字电路设计的差异-就高速数字电路而言,虽然电压还是重点关注对象,但是其设计方法和射频电路的设计方法相近,也需要考虑阻抗阻抗匹配,因为反射电压的存在会导致额外的误码率。

- 关键字:

射频电路 数字电路

- 数字电路之时序电路-在《数字电路之如雷贯耳的“逻辑电路”》、《数字电路之数字集成电路IC》之后,本文是数字电路入门3,将带来「时序电路」的讲解,及其核心部件触发器的工作原理。什么是时序电路?

- 关键字:

数字电路 时序电路 触发器 电路设计

- 高速PCB布线的四大技巧和要领-在高速PCB的设计过程中,布线是技巧最细、限定最高的,工程师在这个过程中往往会面临各种问题。本文将首先对PCB做一个基础的介绍,同时对布线的原则做一个简单讲解,最后还会带来非常实用的四个PCB布线的技巧和要领。

- 关键字:

PCB布线 pcb 数字电路

- 数字电路中的几个基本概念-建立时间(setuptime)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器...

- 关键字:

数字电路 建立时间 保持时间

- 学习FPGA需要注意的几个重要问题-如何学好FPGA呢,很多人很困惑,多数停留在基础位置徘徊,我就这方面问题给大家谈几点自己的看法。

- 关键字:

FPGA 数字电路 HDL语言

- 扫盲贴:模拟电路与数字电路差异化你真的“懂”吗?-作为一位硬件工程师,必须面对的就是两个基本电路:模拟电路和数字电路。下面我们就来了解一下这两个电路的基本知识。 一、模拟电路与数字电路的定义及特点: 模拟信号 处理模拟信号的电子电路。模拟二字主要指电压(或电流)对于真实信号成比例的再现。

- 关键字:

模拟电路 数字电路 模拟信号

- 详细教学高速数字电路经典设计与仿真- 高速数字系统设计成功的关键在于保持信号的完整,而影响信号完整性(即信号质量)的因素主要有传输线的长度、电阻匹配及电磁干扰、串扰等。

- 关键字:

数字电路

数字电路介绍

数字电路

定义:

用数字信号完成对数字量进行算术运算和逻辑运算的电路称为数字电路,或数字系统。由于它具有逻辑运算和逻辑处理功能,所以又称数字逻辑电路。

数字逻辑电路分类

按功能来分:

1、组合逻辑电路

简称组合电路,它由最基本的的逻辑门电路组合而成。特点是:输出值只与当时的输入值有关,即输出惟一地由当时的输入值决定。电路没有记忆功能,输出状态随着输入状态的 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473