- 电源完整性在现今的电子产品中相当重要。有几个有关电源完整性的层面:芯片层面、芯片封装层面、电路板层面及系统层面。在电路板层面的电源完整性要达到以下三个需求:1、使芯片引脚的电压噪声+电压纹波比规格要求要小一些(例如芯片电源管脚的输入电压要求1V之间的误差小于+/-50 mV)2、控制接地反弹(地弹)(同步切换噪声SSN、同步切换输出SSO)3、降低电磁干扰(EMI)并且维持电磁兼容性(EMC):电源分布网络(PDN)是电路板上最大型的导体,因此也是最容易发射及接收噪声的天线。“地弹”,是指芯片内部“地”电

- 关键字:

电容 去耦电容 PCB设计

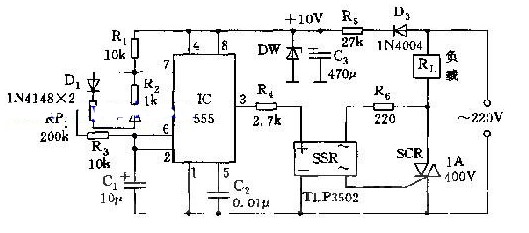

- 电路的设计中存在很多电磁干扰(EMI)问题, 去耦电容的应用场景就是减小电磁干扰,这一过程衍生出了另一个概念 —— 电磁兼容(EMC)。电磁干扰(EMI)的例子1. 静电放电(ESD)冬天的时候,尤其是空气比较干燥的内陆城市,很多朋友都有这样的经历,手触碰到电脑外壳、铁柜子等物品的时候会被电击,这就是 静电放电现象 ,也称之为 ESD 。2. 快速瞬间群脉冲(EFT)不知道有没有同学有这样的经历,早期我们使用电钻这种电机设备,并且同时在听收音机或者看电视的时候,收音机或者电视会出现杂音,这就是

- 关键字:

电磁干扰 去耦电容 EMI EMC

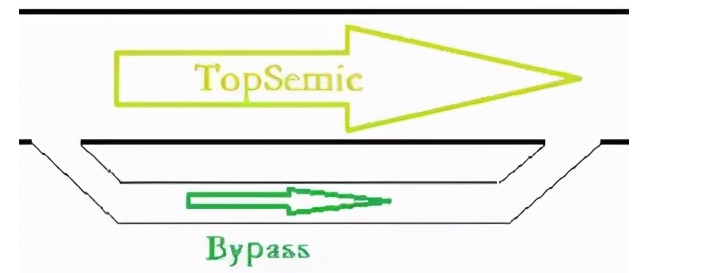

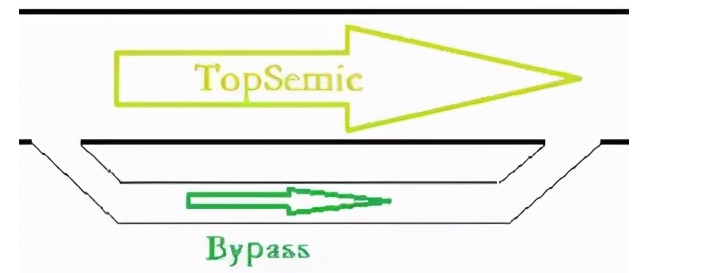

- 今天想和各位电子工程师一起探讨一下怎么区分去耦电容和旁路电容?本来是想自己讲一下的,但发现大佬太多,并且都通俗易懂,我就把分析得很好地总结在一起,供大家讨论和学习。什么是去耦电容和旁路电容?大佬A 匡国华老师:旁路电容,站在芯片的角度,一般都是输入端的滤波。旁路电容把接收来的信号,留下自己需要的,旁路掉高频噪声。旁路电容去藕电容,一般是指信号的输出端的滤波电容旁路电容和去耦电容因为芯片本身是打算产生一个完美的信号,但是里边其他部分的电路太多了,有一部分噪声会“耦合”到它制造的这个信号线上去,输出后用电容把

- 关键字:

去耦电容 旁路电容 电路保护

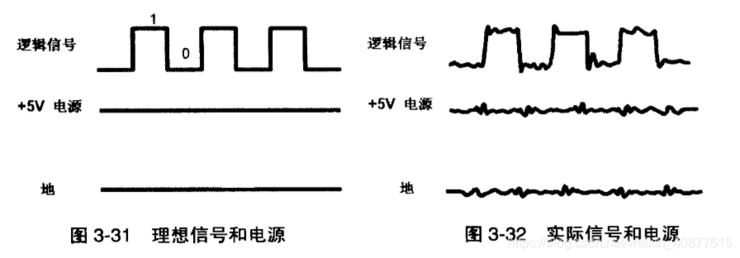

- 峰电流的形成:数字电路输出高电平时从电源拉出的电流Ioh和低电平输出时灌入的电流Iol的大小一般是不同的,即:Iol>Ioh。以下图的TTL与非门为例说明尖峰电流的形成:输出电压如右图(a)所示,理论上电源电流的波形如右图(b),而实际的电源电流保险如右图(c)。由图(c)可以看出在输出由低电平转换到高电平时电源电流有一个短暂而幅度很大的尖峰。尖峰电源电流的波形随所用器件的类型和输出端所接的电容负载而异。产生尖峰电流的主要原因是:输出级的T3、T4管短设计内同时导通。在与非门由输出低电平转向高电平的过程中

- 关键字:

尖峰电流 pcb布局 去耦电容

- 在科学技术高度发达的今天,各种各样的高科技出现在我们的生活中,为我们的生活带来便利,那么你知道这些高科技可能会含有的去耦电容吗? 前段时间有跟大家分享过去耦电容的有效使用方法——“要点一”使用多个去耦电容,今天为大家继续介绍“要点二”降低电容的 ESL(等效串联电感) 在电路板布线上采取措施,使信号线的杂散电容降到最小; 去耦电容的有效使用方法的第二个要点是降低电容的 ESL(即等效串联电感)。虽说是“降低 ESL”,但由于无法改变单个产品的 ESL 本身,因此这里是指“即使容值相同,也要使用 ES

- 关键字:

去耦电容 滤波

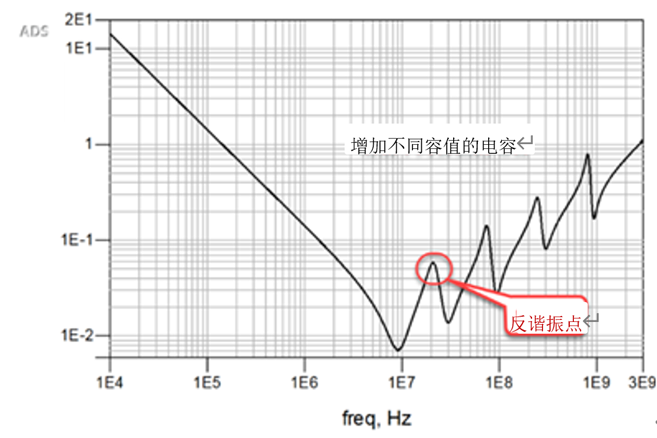

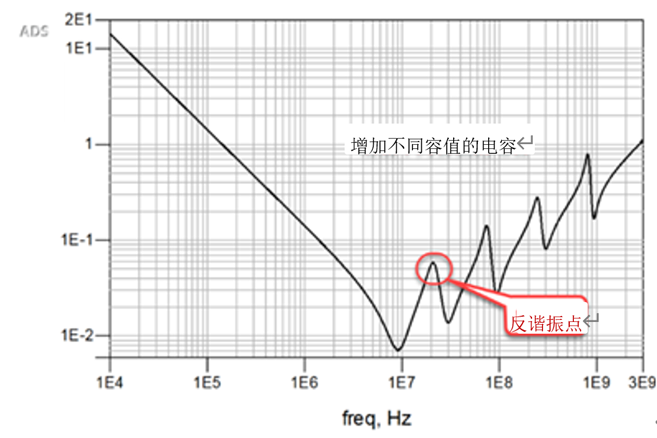

- 在设计普通电路时,工程师们通常关注的是电容的容值、耐压值、封装大小、工作温度范围、温漂等参数。但是在高速电路上或电源系统中及一些对电容要求很高的时钟电路中,电容已经不仅仅是电容,是一个由等效电容、等效电阻和等效电感组成的一个电路,简单的结构如图所示。在设计普通电路时,工程师们通常关注的是电容的容值、耐压值、封装大小、工作温度范围、温漂等参数。但是在高速电路上或电源系统中及一些对电容要求很高的时钟电路中,电容已经不仅仅是电容,是一个由等效电容、等效电阻和等效电感组成的一个电路,简单的结构如图所示。电容在高速

- 关键字:

去耦电容

- 旁路电容(Bypass Capacitor)和去耦电容(Decoupling Capacitor)这两个概念在电路中是常见的,但是真正理解起来并不容易。

- 关键字:

旁路电容 去耦电容

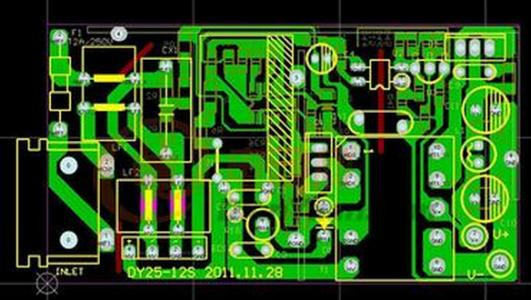

- 设计电路板最基本的过程可以分为三大步骤:电路原理图的设计,产生网络表,印制电路板的设计。不管是板上的器件布局还是走线等等都有着具体的要求。 例如,输入输出走线应尽量避免平行,以免产生干扰。两信号线平行走线必要是应加地线隔离,两相邻层布线要尽量互相垂直,平行容易产生寄生耦合。电源与地线应尽量分在两层互相垂直。线宽方面,对数字电路PCB可用宽的地线做一回路,即构成一地网(模拟电路不能这样使用),用大面积铺铜。 下面这篇文章就单片机控制板PCB设计需要注意的原则和一些细节问题进行了说明。 1.元器件布

- 关键字:

PCB 去耦电容

- 去耦电容器的作用你知道吗?在众多电路设计的应用中都会用到去耦电容器,但设计者也往往嫌麻烦而省略了去耦电容器的使用。不要小看去耦电容器的使用,

- 关键字:

去耦电容 缓冲电路 PCB

- 为了保证高频输入和输出。(这不是说电容能跳Hokey Cokey1。)每个集成电路(IC)都必须使用电容将各电源引脚连接到器件上的地,原因有二:防止噪声影响其

- 关键字:

IC 去耦电容

- 去耦电容的选择不存在与频率的精确对应关系,理论上越大越好,但现实中所有器件都不是理想器件,不论何种电容,ESL、ESR都是必然存在的,于是实际电容

- 关键字:

去耦电容

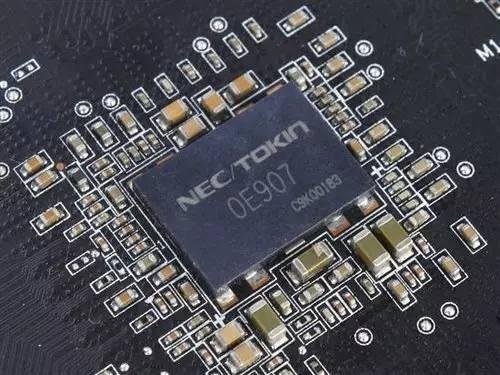

- 对于电容的安装,首先要提到的就是安装距离。容值最小的电容,有最高的谐振频率,去耦半径最小,因此放在最靠近芯片的位置。容值稍大些的可以距离稍远

- 关键字:

PCB布局 尖峰电流 去耦电容

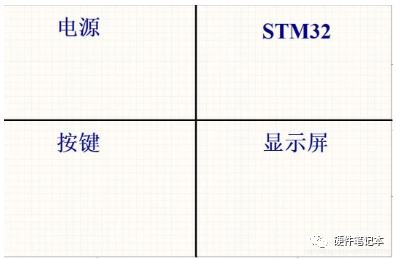

- 在设计中,布局是一个重要的环节。布局结果的好坏将直接影响布线的效果,因此可以这样认为,合理的布局是PCB设计成功的第一步。 尤其是预布局,是思考整个电路板,信号流向、散热、结构等架构的过程。如果预布局是失败的,后面的再多努力也是白费。 1、考虑整体 一个产品的成功与否,一是要注重内在质量,二是兼顾整体的美观,两者都较完美才能认为该产品是成功的。 在一个PCB板上,元件的布局要求要均衡,疏密有序,不能头重脚轻或一头沉。 PCB是否会有变形? 是否预留工艺边? 是否预留MARK点? 是否需

- 关键字:

PCB 去耦电容

- PCB又被称为印刷电路板(Printed Circuit Board),它可以实现电子元器件间的线路连接和功能实现,也是电源电路设计中重要的组成部分。今天就将以本文来介绍PCB板布局布线的基本规则。

元件布局基本规则

1. 按电路模块进行布局,实现同一功能的相关电路称为一个模块,电路模块中的元件应采用就近集中原则,同时数字电路和模拟电路分开;

2.定位孔、标准孔等非安装孔周围1.27mm 内不得贴装元、器件,螺钉等安装孔周围3.5mm(对于M2.5)、4mm(对于M3)内不得贴装元器

- 关键字:

PCB 去耦电容

去耦电容介绍

什么是去耦电容

1,耦合,有联系的意思。

2,耦合元件,尤其是指使输入输出产生联系的元件。

3,去耦合元件,指消除信号联系的元件。

4,去耦合电容简称去耦电容。

5,例如,晶体管放大器发射极有一个自给偏压电阻,它同时又使信号产生压降反馈到输入端形成了输入输出信号耦合,这个电阻就是产生了耦合的元件,如果在这个电阻两端并联一个电容,由于适当容量的电容器对交流信号较小的阻抗(这需要计算 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473