单电源供电的全差分斩波运放电路

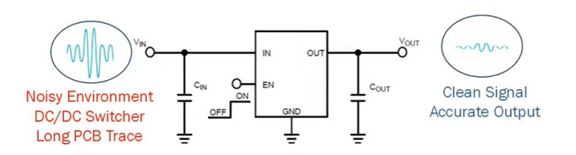

主运放采用全差分折叠式cascode结构,在Class-D的结构中,由于输出功率MOSFET大电流的频繁开启,产生的电磁干扰(EMI)会在电源上形成很强的纹波,在实际应用中发现当芯片工作在5V的电源电压下,EMI引起的电源波动能达到±2V,全差分结构既可以提高运放的电源抑制比和共模抑制比,减弱电源噪声和共模噪声的影响,而且避免了镜像极点,因而对于更大的带宽仍能表现出稳定的特性。

为了提供更高的增益和电压输出摆幅,在fold-cascode后加入共源运放输出级。采用二级运放后.对运放的频率稳定性进行分析。暂时不考虑斩波开关的影响,可以推断该电路至少有三个LHP极点,它们分别是miller补偿电容引入的主极点Wp1,输出滤波电容产生的输出极点Wpout。为第一非主极点,以及folded-cascode(MN1的漏端、MN3的源端)引入的非极点Wp3,三者之间的关系为Wp1

共模反馈电路由MN7~MN10、MP10-MP12构成,输入一端接VDD/2的基准电压,另一端接主运放的共模输出,共模检测电路由电阻和电容构成.经过误差放大后调控主运放的偏置电流。

4 仿真结果及版图设计

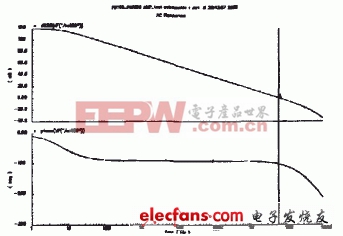

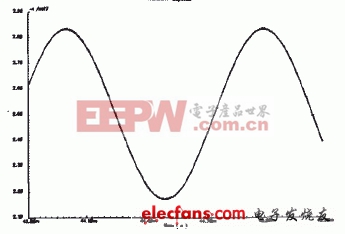

在SMIC O.35微米N阱工艺下.利用cadence spectre工具对本文所设计的电路进行了仿真分析。其中,各器件的工艺参数为典型情况,电源电压5V,输入信号为幅度10uV,频率为1KHz的标准正弦波,斩波频率fch=150K,仿真波形如图5和图6所示。

图5 运放的幅频~相频特性曲线

图6 斩波输出波形

从图5可以看出,在典型情况下,该运放的主极点在10HZ以内,相位裕度75度左右.能充分保证运放在各个comer条件下的稳定性。从输fn波形来看,斩波引起的残余电压尖峰也有了明显的改善。表1为运放的开环仿真结果。

表1 运放开环仿真结果

评论