基于FPGA 的立体LED显示驱动器的设计

系统硬件结构如图1 所示。Nios Ⅱ主端口的时钟是内部总线的时钟,本系统采用50 MHz,用流模式传输的最大带宽能达到100 Mbit/s。在电路设计时,首先用硬件描述语言写用户逻辑,创建Alvalon Slave 接口使之直接和DMA 控制器的主端口相连接, 完成硬件设计。再在Nios Ⅱ IDE 环境下,用C 语言编写DMA 初始化和控制程序,使得流模式的数据传输在FIFO 与Avalon 总线的接口上,能够做到无缝连接。

2.3 立体LED 控制器的设计:

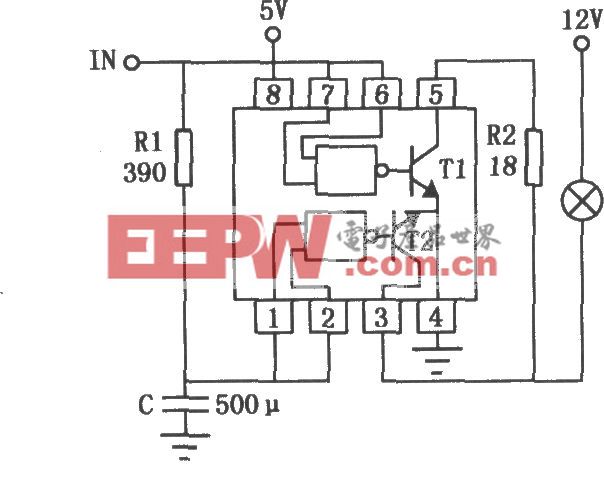

Avalon 流模式LED 控制器硬件结构如图2 所示,用硬件描述语言设计LED 时序发生器, 由于LED 各个像素点的色彩是以RGB 形式的亮度数据用二进制数字方式存储在SDRAM 中的,使用D/T 转换技术[5]即亮度时间转换技术就可以实现LED 屏的全彩显示。笔者设计了一个专用的函数f(i),用此函数即可统一控制各个像素点实现全屏幕所有像素点相互独立而又同步的D/T 转换。这里,f(i)作为LED_latch 信号。

图2 Avalon 流模式LED 控制器结构图

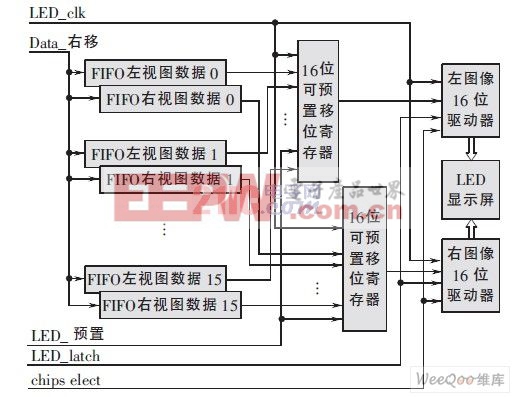

因为FIFO 中的数据格式是左、右视图列交叉显示,因此LED 控制驱动器的设计是以列驱动的。LED 时序发生器的设计如图3 所示,将立体图像对中左、右眼图像帧每个像素的数据用乒乓开关控制存储在FIFO 缓存之中,以16 个列像素点的驱动为例,FIFO 缓存之中的左、右视频数据分别各连接一个16 位可预置移位寄存器,通过16 个时钟脉冲的移位产生16 个像数的驱动数据,由片选信号选择显示行数,由D/T 转换函数f(i)作为LED_latch信号锁存,FIFO 缓存的数据经过8 次移位即可完成1 个像素的真彩驱动。

图3 LED 时序发生器内部结构图

每帧画面显示1 个立体像素真彩信号的时间需要移位8 次, 即250 个基本周期。如果LED 大屏幕显示器每秒最多显示30 帧, 采用1/8 驱动模式和立体像素的1/2时分复用, 再考虑选用16 位移位锁存LED 恒流驱动电路,实际要求的时钟频率为2 MHz。

3 系统软件设计与仿真:

软件设计就是利用SoPC Builder 生成软件文件,用文本编辑器编写汇编语言或C/C++源程序,用GUNPro 将源程序编译成可执行文件, 并通过下载电缆对可执行程序进行调试和运行。软件系统分为两部分:主程序和中断服务程序。主程序主要完成系统的初始化,其主要功能是:对于系统中的每一个微处理器,从设备都生成一个定义该设备地址的头文件,为软件开发创建存储器映射文件。DMA 的操作都通过中断服务程序执行,把需要送出的像素信息排成一行顺序送出形成数据流,借助于Avalon 流模式外设的设计方法, 实现一个Avalon 流模式的LED 控制器。利用DMA 控制器在流模式控制器和SRAM 之间建立一条DMA 传送通道, 让硬件来完成像素信息的自动读取。软件流程如图4 所示,部分内部时序仿真如图5 所示。

评论