关于你的PCB走线长度:多长才算太长?

偶尔,我会从读者那里得到一个问题,激起我的兴趣,最后引发一场激烈的辩论、研究或问答环节。最近我收到的一个问题涉及PCB走线长度、信号标准和组件规格。下面是一个释义的问题:

这总是一个有趣的问题,因为它可以从多个角度来解决。在这种情况下,组件在标准层压板上高速运行在PCIe上(在带宽的高端,Dk~4和Df~0.02)。不难看出,问题在于增加从边缘连接器到接收器的迹线长度,以及组件是否能够容忍增加的距离,并且仍然在信道中恢复信号。

您将如何着手调查在这个通道中您可以容忍的最大PCB跟踪长度?事实上,由于多种原因,任何信令标准都没有一个最大PCB跟踪长度值。相反,我们必须观察信号传播时信道中的损耗。在这个特别的部分,答案是相当令人惊讶的。继续阅读以了解更多。

答案是:看看全损两个元件之间可以放置的最大PCB跟踪长度取决于多个因素。其中包括:

信号协议:信令标准规定了互连设计应达到的最低性能水平。这些需求并不能保证设计能够工作,但它们确实为您提供了一个基线,可以用于设计目标。

组件规格:有些组件可以满足信令标准中的要求,但这仍然不能保证信道正常工作。

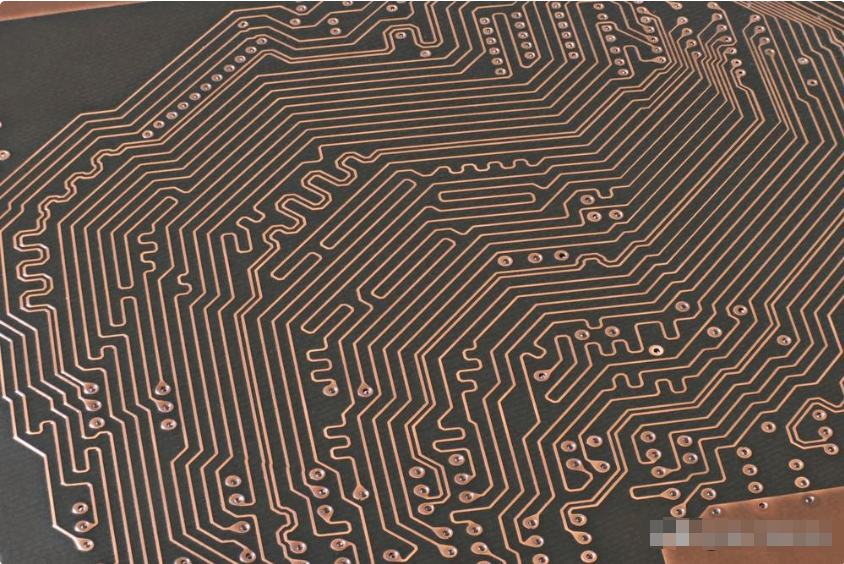

PCB层压板和损耗:所有损失PCB层压板会降低信号幅度并产生失真,因此在确定迹线长度时需要包括这些损耗源。

倾斜和相位失真:在某些情况下,由于光纤编织效应,斜交会累积,这取决于路由路径。这在占据~20ghz和更高频率的信号部分中是最有问题的信号中的相位失真 .

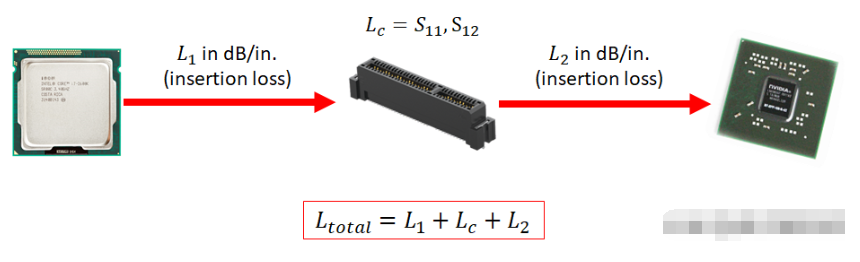

考虑到所有这些,让我们看看损失在英吉利海峡的累积情况。下图显示了我们所考虑的示例信道中的总损耗。这些损失中有一部分是沿着痕迹的长度集中起来的。不管损耗来自何处,我们只需将它们加起来,以分贝为单位,如果愿意,我们可以将其转换回十进制衰减值。

这里的重点是:我不在乎这些损失是从哪里来的,它们加在一起会限制到达接收器的功率。因为信号在变得不可恢复之前只能承受这么大的损失全损将PCB跟踪长度限制为某个最大值。

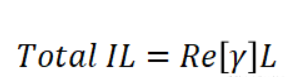

累积损耗插入沿单个记录道的插入损耗(以dB为单位)取决于长度,并与传播常数的长度和实部有关:

只要你知道传播常数和互连长度,你就知道总损耗;它只是插入损耗加上沿着互连的每个接口的回波损耗。如果需要,您可以翻转插入损耗的关系,并确定可接受的损耗和最大跟踪长度(只要您可以确定传播常数)。

如果指定了长度怎么办?让我们回到最初的问题上来。在这个交换中,接收器组件以时间来指定最大PCB跟踪长度,而不是以损失预算或字面跟踪长度来指定。换句话说,他们假设你知道群/相速度(或传播延迟)对于在互连上传输的信号。如果你知道分散,那么你就知道你必须这样做PCB跟踪长度匹配与频率因为信号的速度随频率变化。

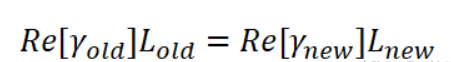

无论您看到指定的特定长度还是指定的时间,这两个值都将仅适用于特定的PCB层压板和跟踪几何图形。如果使用不同的PCB层压材料或迹线几何体,则长度值不再有效,因为沿该迹线长度经历的损耗将不同。在这种情况下,您需要使用与互连上的最大损耗相对应的传播常数将指定的最大PCB跟踪长度转换为新的跟踪长度。您可以使用以下比率:

哪里γ 是信号的传播常数,L是长度值。在这里,我得到了γ 这告诉我们沿互连的损耗。如果你看看上面的第一个等式,你应该很容易看到左手边只是一个损失预算。将这些值与传播常数的适当值一起使用,可以得到新的最大PCB跟踪长度。

模拟和场解算器可以提供帮助在设计级别可以采取一些步骤来增加允许的迹线长度,以防止过度损耗:

使用低损耗材料,如聚四氟乙烯层压材料

选择损耗更低的连接器

移除多余的过孔和背刺钻

尝试修改轨迹几何体,使其具有较低的损耗

如果给了互连的时间或长度约束,则只需要新旧互连的传播常数来确定新的长度。如果您使用的是Altium Designer,您可以使用Layer Stack Manager来计算阻抗控制网络的传播延迟,并且可以使用它来设置相关网络类的跟踪长度限制。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。