日常应用笔记:如何使用这些 PCB 设计指南降低 EMI

电磁干扰 (EMI) 无处不在,无论是来自人造电子电路还是来自大气中的宇宙辐射。过量时,EMI 会破坏敏感的电子设备。我们不是在这里谈论您的智能手机。想想负责维持病人生命的医疗设备。或者在公共交通系统中使火车保持在正确轨道上的系统。

由于这种危险,我们对各种电子设备中的 EMI 辐射制定了一些严格的要求。FCC 第 15 部分就是其中之一。作为电子设计师,这一切对您意味着什么?事实是,每个电子设备都会发出某种 EMI。解决方案不是完全消除它,而是通过一些精心策划的 PCB 设计指南来减少它。这就是德州仪器的日常应用笔记的全部内容。

设计具有低电磁干扰的系统并非不可能,但它需要一组您可能不具备的工程知识。您是否在不知不觉中在您的 PCB 布局上创建了可以辐射电磁能量的天线?也许你甚至不知道你必须关心你的信号返回路径?你可能有一些问题需要解决。

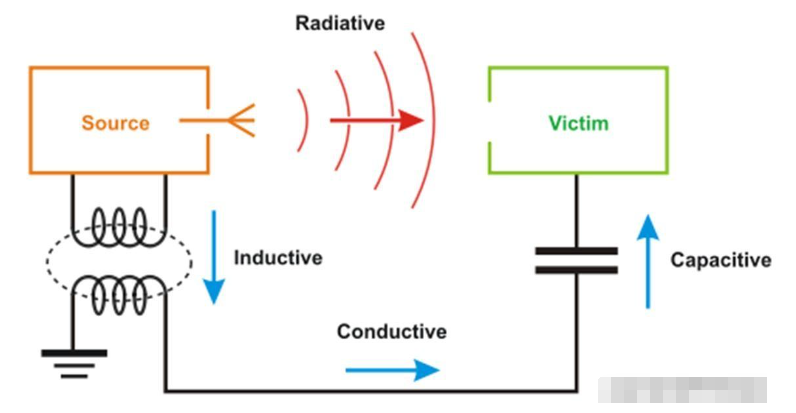

EMI 一览。

本应用笔记通过大量 PCB 设计指南保持其实用性,您现在可以在设计项目中实施这些指南。从接地层和电源层到信号走线和屏蔽层,向您的新 EMI Premier 打个招呼。以下是您可以在其中找到的一些设计指南的简要示例:

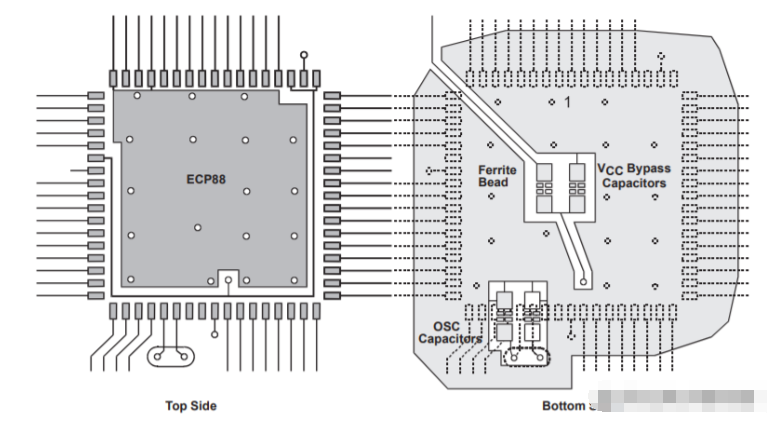

接地微型计算机您需要在微型计算机下方的底层有一个接地区域作为噪声过滤器。该区域应超出设备轮廓 1/4 英寸。接地区域还需要覆盖振荡器引线和任何电源旁路电容器。

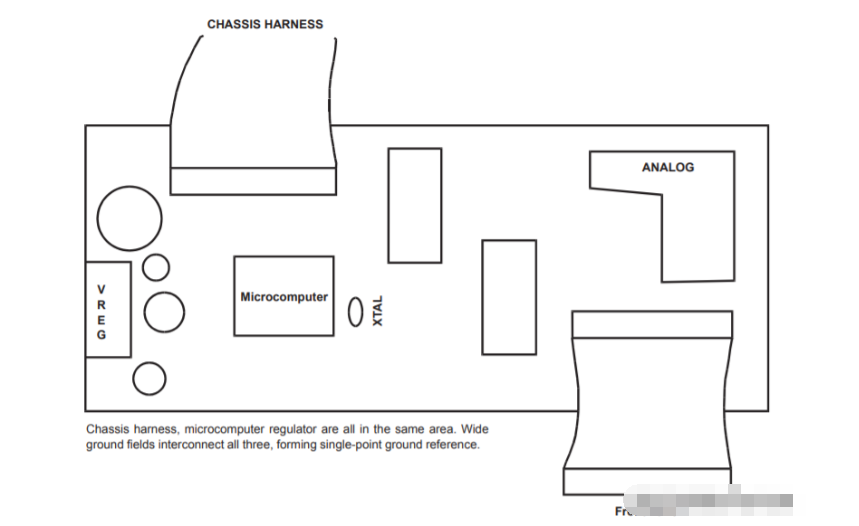

提前考虑根据功能规划电路板的布局将有助于降低 EMI。您可以将其视为平面图,即 10,000 英尺的视图。高速逻辑应靠近电源,但远离慢速/模拟组件。这确保了高速逻辑不会干扰其他信号走线。

如果设计得当,两层板可以与四层板一样有效。在这些布局堆栈中,为直接连接到信号迹线下的处理器 I/O 布线返回非常重要。您还需要小心,切勿在电路板的隔离区域中布线,例如高功率和数字接地之间的区域。

立即阅读随着 IC 器件的速度和密度不断提高,您一定会发现本应用笔记中的所有指南对项目都有用。今天就来熟悉一下它们,这样当 EMI 来袭时,您就可以做好准备了!

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。