三星成立特别小组,强攻先进封装

来源:内容来自半导体芯闻(ID:MooreNEWS)综合自businesskorea等,谢谢。

据韩国媒体businesskorea报道,三星电子今日成立了半导体封装工作组 (TF),该部门直属DS业务部门负责人Kyung Kye-hyun,直接向CEO汇报,旨在加强与封装领域大型代工客户的合作。

报道进一步指出,该团队由 DS 部门测试与系统封装 (TSP) 的工程师、半导体研发中心的研究人员以及公司内存和代工部门的相关工作人员组成。该团队预计将提出先进的封装解决方案,以加强与客户的合作。

Kyung 的举动表明了他对先进半导体封装技术的重视。封装是指将完成前端工艺的晶圆切割成半导体的形状或对其进行布线。在业界,它也被称为“后段制程”。

如今,随着前端工艺中的小型化电路工作已达到极限,将芯片连接起来并使其作为单个半导体运行的所谓“3D封装”或“小芯片”技术正受到关注。

尤其是英特尔和台积电等全球半导体巨头正在大举投资先进封装。根据市场研究公司 Yole Development 的数据,英特尔和台积电分别占 2022 年全球先进封装投资的 32% 和 27%。三星电子排名第四,仅次于台湾后端工艺公司 ASE。

英特尔已经在 2018 年推出了名为“Foveros”的 3D 封装品牌,并宣布将把这项技术应用到各种新产品中。它还设计了一种将每个区域组装成产品的方法,将其制作成tiles。2020 年发布的一款名为“Lakefield”的芯片就是采用这种方式制成的,并安装在三星电子的笔记本电脑中。

台积电最近也决定使用这项技术生产其最大客户 AMD 的最新产品。英特尔和台积电非常积极地在日本建立了一个 3D 封装研究中心,并从 6 月 24 日开始运营。

三星也在这个市场发力,在 2020 年推出了 3D 堆叠技术“X-Cube”。三星电子晶圆代工事业部总裁 Choi Si-young 在 Hot Chips 2021 上表示正在开发“3.5D 封装”去年六月。半导体行业的注意力为零,三星的这个工作组是否能够找到一种方法,使三星与该领域的竞争对手保持领先。

韩媒:三星重估先进封装策略

台积电今年资本支出拉高至400至440亿美元除全力提升制程技术与产能外,台积电也积极布局先进封测领域,甚至传出有意前往嘉义设封测厂,力拼提供客户一条龙服务。反观,韩媒披露,三星内部将重新评估设立先进封装扇出型晶圆级封装(FOWLP)产线的计划,最主要原因是,即使该产线建置完成,目前三星并没有可靠的大客户能确保产能,可能导致封装产线使用率低落。

《TheElec》报导,消息人士指出,三星原本打算在天安市投资2000亿韩元,建立先进封装扇出型晶圆级封装(FOWLP)产线,并将技术运用在旗下Exynos系列的处理器生产上,但近期的高层会议却对此事提出质疑。

报导指出,高层们认为,即使建立出一条FOWLP生产线,该生产线并无法获得充分利用,主因是目前没有可靠的大客户,可以保证对封装产线的需求。此外,主要潜在客户三星移动(Samsung Mobile)与高通(Qualcomm)的接受度也不高。

此外,客户们认为,使用传统PoP封装技术就能提高处理器的性能,且整体成本也低于FOWLP封装,导致目前客户并没有太大兴趣。不仅如此,三星天安工厂现有的PLP生产线也没有达到三星预期,目前该产线主要用在Galaxy Watch系列等智能手表的芯片封装。

目前三星内部仍未对此计划做出最终决定,而若该计划顺利进行,会先用于最近推出的Exynos 2200行动处理器的后续产品,且消息人士也认为,无论如何,三星仍会寻求扩大FOWLP的生产技术。

先进封装:谁是赢家?谁是输家?

近年来,因为传统的晶体管微缩方法走向了末路,于是产业便转向封装寻求提升芯片性能的新方法。例如近日的行业热点新闻《打破Chiplet的最后一道屏障,全新互联标准UCIe宣告成立》,可以说把Chiplet和先进封装的热度推向了又一个新高峰?

那么为什么我们需要先进封装呢?且看Yole解读一下。

为什么我们需要高性能封装?

随着前端节点越来越小,设计成本变得越来越重要。高级封装 (AP) 解决方案通过降低成本、提高系统性能、降低延迟、增加带宽和电源效率来帮助解决这些问题。

高端性能封装平台是 UHD FO、嵌入式 Si 桥、Si 中介层、3D 堆栈存储器和 3DSoC。嵌入式硅桥有两种解决方案:台积电的 LSI 和英特尔的 EMIB。对于Si interposer,通常有台积电、三星和联电提供的经典版本,以及英特尔的Foveros。EMIB 与 Foveros 结合产生了 Co-EMIB,用于 Intel 的 Ponte Vecchio。同时,3D 堆栈存储器由 HBM、3DS 和 3D NAND 堆栈三个类别表示。

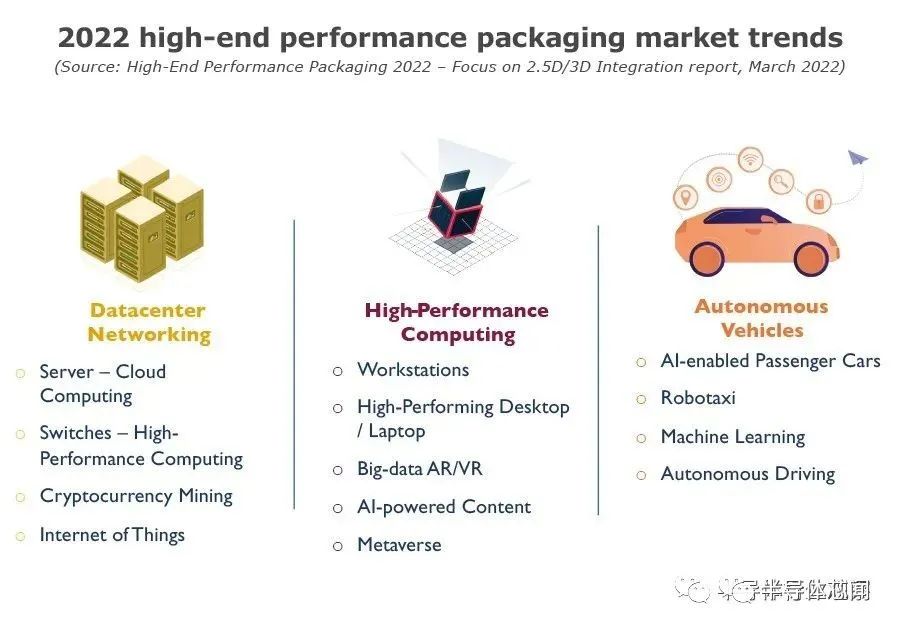

数据中心网络、高性能计算和自动驾驶汽车正在推动高端性能封装的采用,以及从技术角度来看的演变。今天的趋势是在云、边缘计算和设备级别拥有更大的计算资源。因此,不断增长的需求正在推动高端高性能封装的采用。

高性能封装市场规模?

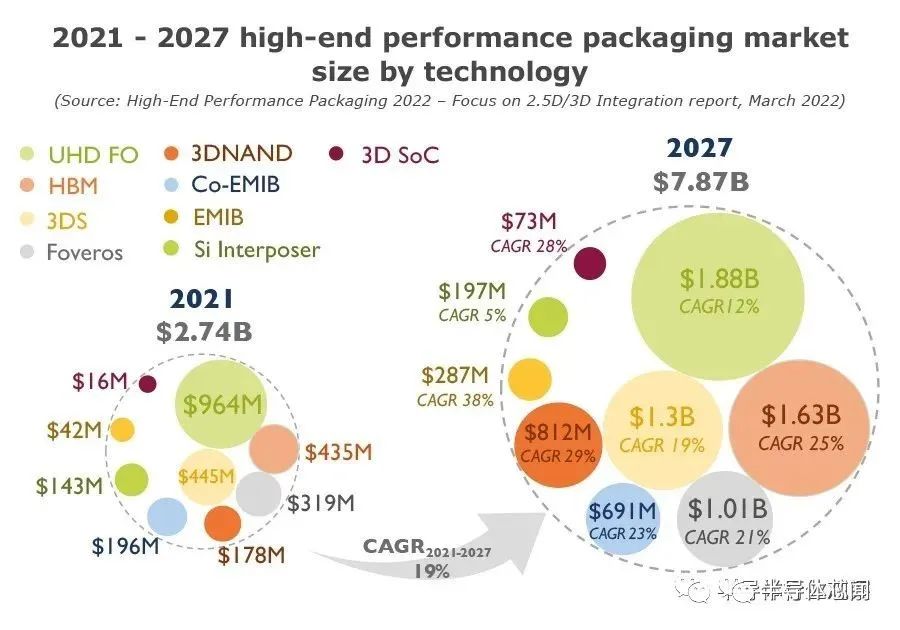

据Yole预测,到 2027 年,高性能封装市场收入预计将达到78.7亿美元,高于 2021 年的27.4亿美元,2021-2027 年的复合年增长率为 19%。到 2027 年,UHD FO、HBM、3DS 和有源 Si 中介层将占总市场份额的 50% 以上,是市场增长的最大贡献者。嵌入式 Si 桥、3D NAND 堆栈、3D SoC 和 HBM 是增长最快的四大贡献者,每个贡献者的 CAGR 都大于 20%。

由于电信和基础设施以及移动和消费终端市场中高端性能应用程序和人工智能的快速增长,这种演变是可能的。高端性能封装代表了一个相对较小的业务,但对半导体行业产生了巨大的影响,因为它是帮助满足比摩尔要求的关键解决方案之一。

谁是赢家,谁是输家?

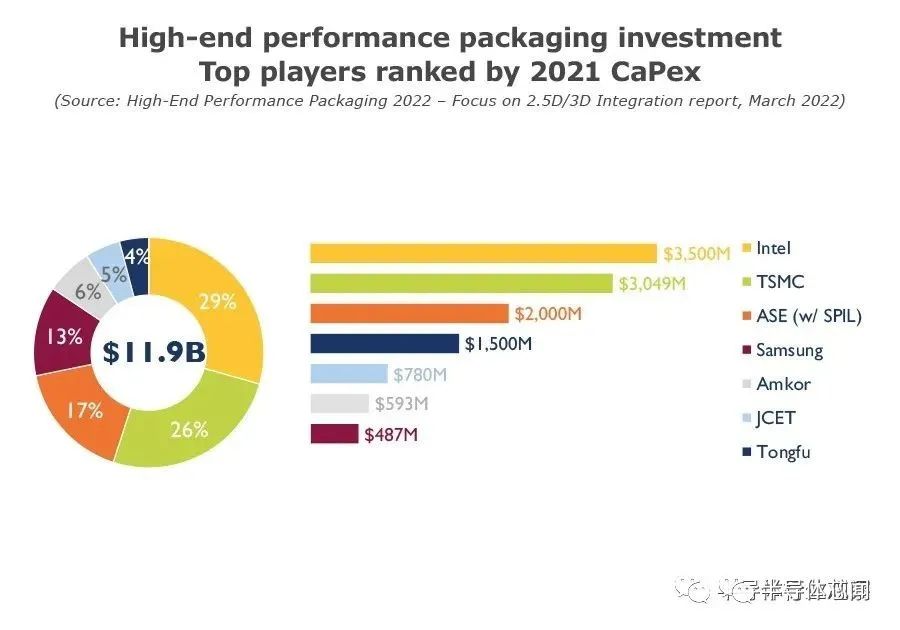

2021 年,顶级参与者为一揽子活动进行了大约116亿美元的资本支出投资,因为他们意识到这对于对抗摩尔定律放缓的重要性。

英特尔是这个行业的最大的投资者,指出了35亿美元。它的 3D 芯片堆叠技术是 Foveros,它包括在有源硅中介层上堆叠芯片。嵌入式多芯片互连桥是其采用 55 微米凸块间距的 2.5D 封装解决方案。Foveros 和 EMIB 的结合诞生了 Co-EMIB,用于 Ponte Vecchio GPU。英特尔计划为 Foveros Direct 采用混合键合技术。

台积电紧随其后的是 30.5亿美元的资本支出。在通过 InFO 解决方案为 UHD FO 争取更多业务的同时,台积电还在为 3D SoC 定义新的系统级路线图和技术。其 CoWoS 平台提供 RDL 或硅中介层解决方案,而其 LSI 平台是 EMIB 的直接竞争对手。台积电已成为高端封装巨头,拥有领先的前端先进节点,可以主导下一代系统级封装。

三星拥有类似于 CoWoS-S 的 I-Cube 技术。三星是 3D 堆栈内存解决方案的领导者之一,提供 HBM 和 3DS。其 X-Cube 将使用混合键合互连。

ASE 估计为先进封装投入了 20 亿美元的资本支出,是最大也是唯一一个试图与代工厂和 IDM 竞争封装活动的 OSAT。凭借其 FoCoS 产品,ASE 也是目前唯一具有 UHD FO 解决方案的 OSAT。

其他OSAT 不具备在先进封装竞赛中与英特尔、台积电和三星等大公司并驾齐驱的财务和前端能力。因此,他们是追随者。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。

路由器相关文章:路由器工作原理

路由器相关文章:路由器工作原理

激光器相关文章:激光器原理