- 数字电路之时序电路-在《数字电路之如雷贯耳的“逻辑电路”》、《数字电路之数字集成电路IC》之后,本文是数字电路入门3,将带来「时序电路」的讲解,及其核心部件触发器的工作原理。什么是时序电路?

- 关键字:

数字电路 时序电路 触发器 电路设计

- 在FPGA/CPLD设计中,状态机是最典型、应用最广泛的时序电路模块,如何设计一个稳定可靠的状态机是我们必须面对的问题.

- 关键字:

时序电路 状态机 FPGA

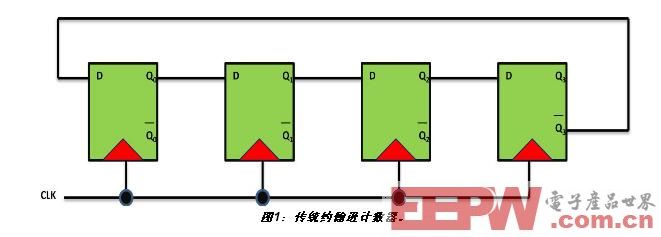

- 在传统设计中,所有计算机运算(算法、逻辑和存储进程)都参考时钟同步执行,时钟增加了设计中的时序电路数量。在这个电池供电设备大行其道的移动时代,为了节省每一毫瓦(mW)的功耗,厂商间展开了残酷的竞争,因此将电路分成多个电源域并根据要求关闭它们,并且在设计每个时序电路的同时节省功耗,这两点至关重要。时序电路(如计数器和寄存器)在现代设计中无处不在。本文以约翰逊计数器为例介绍了如何采用有效门控时钟来设计高能效的时序电路。

约翰逊计数器系统,可同步提供多种特殊类型的数据序列,这对于大多数重要应用(如D/

- 关键字:

门控时钟 时序电路 触发器

- 摘要:为了实现时序电路状态验证和故障检测,需要事先设计一个输入测试序列。基于二叉树节点和树枝的特性,建立时序电路状态二又树,按照电路二叉树节点(状态)与树枝(输入)的层次逻辑关系,可以直观和便捷地设计出时

- 关键字:

二叉树 测试序列 时序电路

- 在SSI时序逻辑电路设计中,遵循的设计准则是:在保证所设计的时序逻辑电路具有正确功能的前提下,触发器的激...

- 关键字:

SSI 数据选择器 D触发器 时序电路

- 文中较为详细地介绍了TDI-CCD的结构和工作原理,并根据工程项目所使用的IL-E2 TDI-CCD的特性,设计了一种基于现场可编程门阵列 (FPGA) 的TDI-CCD时序电路

- 关键字:

FPGA CCD TDI 时序电路

时序电路介绍

时序逻辑电路简称时序电路

时序电路,它是由最基本的逻辑门电路加上反馈逻辑回路(输出到输入)或器件组合而成的电路,与组合电路最本质的区别在于时序电路具有记忆功能。时序电路的特点是:输出不仅取决于当时的输入值,而且还与电路过去的状态有关。它类似于含储能元件的电感或电容的电路,如触发器、锁存器、计数器、移位寄存器、储存器等电路都是时序电路的典型器件。

时序逻辑电路的状态是由存储电路来记忆 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473