- 介绍了一种基于FPGA的多轴控制器,控制器主要由ARM7(LPC2214)和FPGA(EP2C5T144C8)及其外围电路组成,用于同时控制多路电机的运动。利用Verilog HDL硬件描述语言在FPGA中实现了电机控制逻辑,主要包括脉冲控制信号产生、加减速控制、编码器反馈信号的辨向和细分、绝对位移记录、限位信号保护逻辑等。论文中给出了FPGA内部一些核心逻辑单元的实现,并利用QuartusⅡ、Modelsim SE软件对关键逻辑及时序进行了仿真。实际使用表明该控制器可以很好控制多轴电机的运动,并且能

- 关键字:

VerilogHDL FPGA 多轴控制器 编码器 四细分

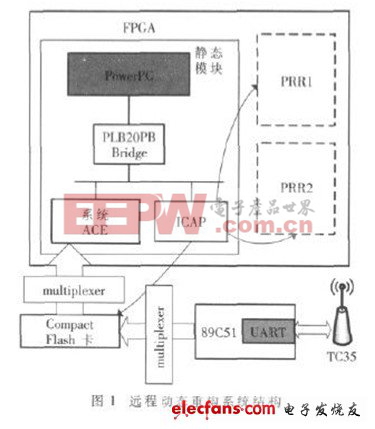

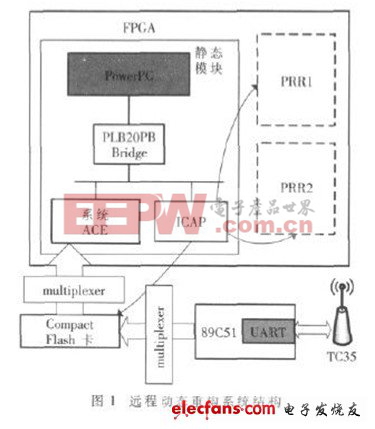

- 随着现场可编程门阵列的广泛应用,对其进行灵活的重新配置的研究也越来越多。目前绝大多数FPGA都是基于查找表LUT(Look UP Table)的技术,采用SRAM工艺生产。这种工艺的FPGA有两层结构,上层为配置存储器,下层是

- 关键字:

滤波器 设计 实现 数字 FIR VerilogHDL 语言 基于

- VerilogHDL综合性设计 1 时钟安排 选用上升沿触发的单时钟信号,尽量不使用混合触发的时钟信号。因为时钟周期在时序分析的过程中是关键问题,它还影响到时钟的频率。使用简单的时钟结构 利于时钟信号的分析和保持

- 关键字:

设计 综合性 VerilogHDL

- 现代计算机和通信系统中广泛采用数字信号处理的技术和方法,其基本思路是先把信号用一系列的数字来表示,然后对...

- 关键字:

滤波器 VerilogHDL

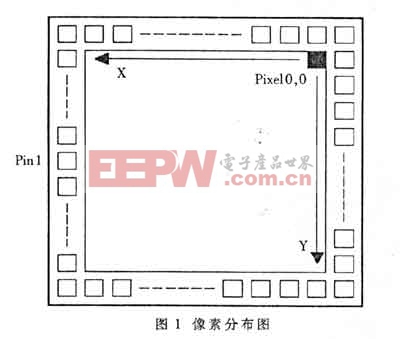

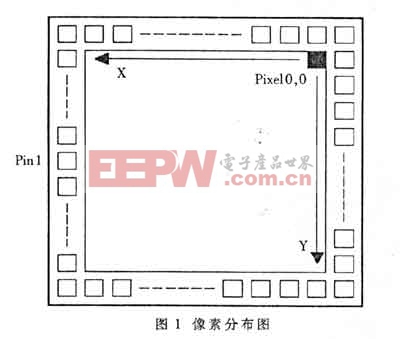

- Verilog HDL语言是IEEE标准的用于逻辑设计的硬件描述语言,具有广泛的逻辑综合工具支持,简洁易于理解。本文就STAR250这款CMOS图像敏感器,给出使用Verilog HDL语言设计的逻辑驱动电路和仿真结果。

- 关键字:

驱动 电路设计 敏感 图像 VerilogHDL CMOS 基于

- 0 引 言

现代计算机和通信系统中广泛采用数字信号处理的技术和方法,其基本思路是先把信号用一系列的数字来表示,然后对这些数字信号进行各种快速的数学运算。其目的是多种多样的,有的是为了加密,有的是为了去

- 关键字:

VerilogHDL 小波滤波器

- 本文介绍了一种基于硬件描述语言VerilogHDL的背景噪声扣除电路设计,该设计与以往使用加减计数芯片组成的电路相比,具有与MCU接口简单,软件操作方便等优点。

- 关键字:

VerilogHDL 背景 电路设计

veriloghdl介绍

您好,目前还没有人创建词条veriloghdl!

欢迎您创建该词条,阐述对veriloghdl的理解,并与今后在此搜索veriloghdl的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473