- 该篇将分析对象限定为一个DAC,其中的输出缓冲器在正常模式下被加电:零量程或中量程。文章将分析一下DAC输出在高阻抗模式中被加电的情况。同时提出一个针对加电毛刺脉冲的数学模型,随后给出一个尽可能减少此毛刺脉

- 关键字:

DAC 加电 断电

- 摘要:主要介绍了一种高稳定性恒流源系统的设计方案,该系统在负载为1Omega;~15Omega;时,恒流输出可调范围0A~1A,且恒流源电流可以在该范围内任意设定,精度为plusmn;3mA。该恒流源系统主要由PIC单片机电路、A

- 关键字:

PIC单片机 ADC DAC 恒流源

- 本文章是关于ADC/DAC设计经典问答,涵盖时钟占空比、共模电压、增益误差、微分相位误差、互调失真等常见问题。

1. 什么是小信号带宽(SSBW)?

小信号带宽(Small Signal Bandwidth (SSBW))是指在指定的幅值输入信号及特定的频率下,它的输出幅值比低频时的输出幅值下降指定值时,该特定频率为小信号带宽。

2. 什么是共模电压(VCM)?

共模电压(Common Mode Voltage (VCM ))是差动输入的两个引脚上相同的直流输入电压。

3

- 关键字:

ADC DAC

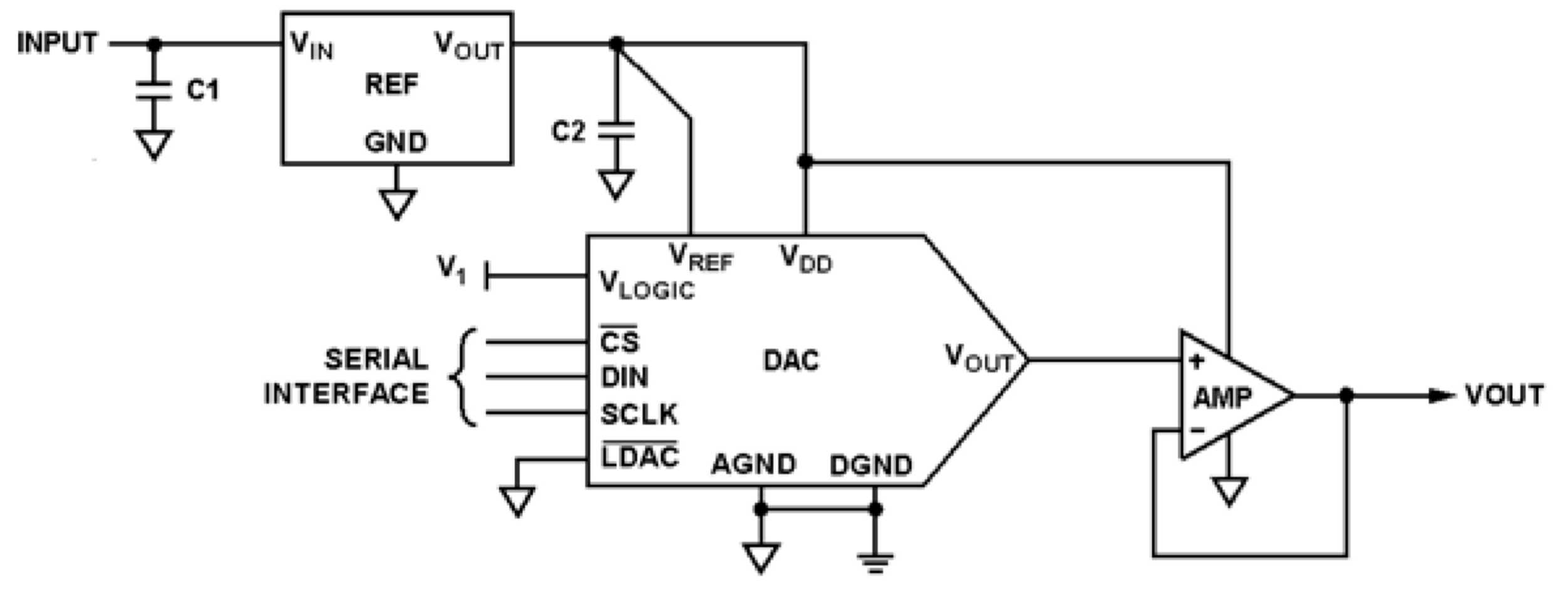

- 数模转换器广泛用于各种应用中,并常常搭配放大器使用,以便对输出信号进行调理。 放大器可以提升输出电流驱动能力、将差分信号转换为单端输出信号、隔离下游信号路径,或者提供互补双极性输出电压。 图1显示的是单电源供电的典型信号链,由基准电压源、数模转换器和缓冲器组成。 为了保持高动态输出范围和高信噪比性能,数模转换器(DAC)通常设计为可工作在全摆幅状态下,而基准电压(VREF)设为与电源电压(VDD)相等。 这样可以最大程度利用数字码。 采用单电源时,DAC和输出缓冲器电源通常连接到同一条电源线上。 在这

- 关键字:

放大器 DAC

- 本文章是关于ADC/DAC设计经典问答 。 1. 什么是小信号带宽(SSBW)? 小信号带宽(Small Signal Bandwidth (SSBW))是指在指定的幅值输入信号及特定的频率下,它的输出幅值比低频时的输出幅值下降指定值时,该特定频率为小信号带宽。 2. 什么是共模电压(VCM)? 共模电压(Common Mode Voltage (VCM ))是差动输入的两个引脚上相同的直流输入

- 关键字:

ADC DAC

- 所有DAC之间的共性就是技术规格的定义以及说明。这篇文章将会论述静态DAC技术规格。静态DAC技术规格包括对DAC在DC域中所具有的特性的描述。在DC域中时,DAC的数字与模拟定时现象不属于这一组技术规格。

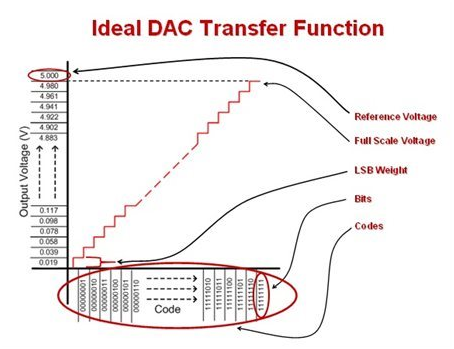

图1 虽然这3个DAC拓扑互不相同,但它们的技术规格与电气描述非常类似。 一个主要的静态DAC技术规格就是理想转换函数(图2)。在对这个普通转换函数的图示中,可以轻松地体会和理解零代码、偏移、满量程以及增益的定义。一旦你理解了上述概念,差分非线性&

- 关键字:

DAC 静态技术

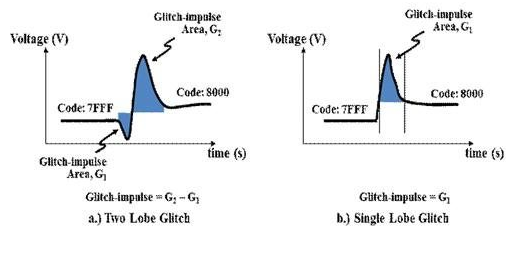

- 在使用数模转换器 (DAC) 进行设计时,您肯定希望输出能够从一个值向另一个值单调转换,但实际电路并不总是以这种方式工作的。 在某些特定代码范围内出现过冲与下冲(即干扰脉冲)也很平常。这些脉冲会以这两种形式中的一种出现,如图 1 所示。

图1:DAC干扰行为 图 1a 是一种可产生两个代码转换误差区的干扰,在R-2R 高精度 DAC中很常见。图 1b 是

- 关键字:

DAC R-2R

- 当我们在专门研究模数转换器(ADC)、运算放大器(OpAmp)、数模转换器(DAC)以及其他电子架构的工程类院校修完其主干课程以后,您可能会认为您已理解了这些电路的所有基本功能。大多数人均对ADC的工作原理有了一个很好的了解,但是对DAC的工作原理却不太熟悉,它究竟有何功能呢?同样,对于大多数人来说,DAC只不过是一个输入端为数字信号数据而输出端为模拟信号数据的“黑匣子”。只有为数不多的人知道其在架构方面的区别,以及与R2R梯形架构相比一个电阻串架构(stringarchitecture)所具有的优点

- 关键字:

R2R DAC

- 简介 本应用笔记描述一个集ADP5070 DC-DC开关稳压器、ADP7142和ADP7182互补金属氧化物半导体(CMOS)低压差(LDO)线性稳压器、LC滤波器及电阻分压器于一体的电路,用以从5 V单电压源产生双电源。AD5761R是一款双极性数模转换器(DAC),需要双电源以提供双极性输出电压范围。本应用笔记详细说明了如何配置该电路以使其适合只有一个5 V单电源可用的仪表应用。 作为双极性DAC的单极性5 V电源解决方案,ADP5070、ADP7142

- 关键字:

ADP5070 DAC

- 本文主要介绍了ADC和DAC常用的56个技术术语,如“采集时间”、“混叠”、“孔径延迟”等,帮助初学者更好的理解专业术语。 采集时间 采集时间是从释放保持状态(由采样-保持输入电路执行)到采样电容电压稳定至新输入值的1 LSB范围之内所需要的时间。采集时间(Tacq)的公式如下:

混叠 根据采样定理,超过奈奎斯特频率的输入信号频率为“混叠”频率。也就是说,这些频率被“折叠”或复制到奈奎斯特频率附近的其它频谱位置。为防止混叠,必须对所有有害信

- 关键字:

ADC DAC

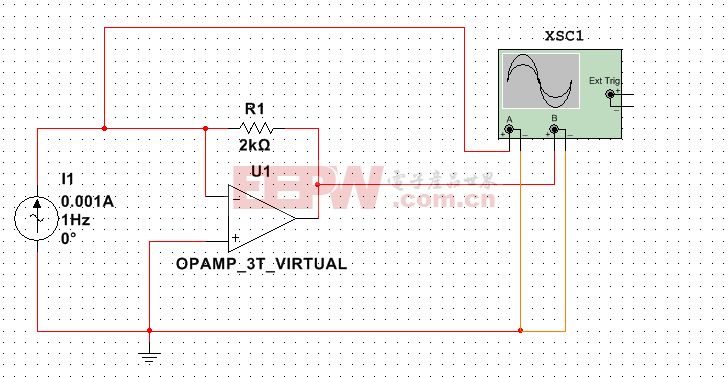

- 作为电子工程师,在职业生涯中会碰到各种各样的问题,其作用就是利用所学的知识解决各种问题。当进行以电流形式输出的传感器电路设计时,通常会通过以下的步骤进行设计:首先电流转换为电压,然后进行电压变换使其适合MCU处理的电压范围。从上面的步骤看出电流转换电压是电流形式输出传感器设计的一个重点。下文将从简单到复杂进行电流转电压电路的分析。 首先,看下经典的电流转换电压静电电路,通常使用一个运放和一个反馈电阻进行设计,如下图所示: 当设置输入电流源为1Hz电流强度为1mA时,在multisim上仿真结果如下

- 关键字:

multisim DAC

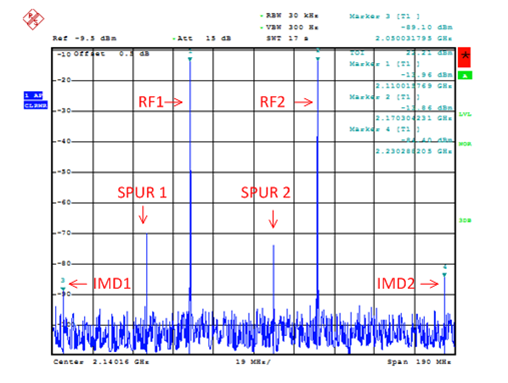

- 最近评估了 TRF3720 全面集成型 IQ 调制器和 PLL/VCO 线性性能。在测量 OIP3 性能时,观察到了出乎预料的寄生信号,如图 1 所示。经与同事讨论,我们得出的结论是数模转换器 (DAC) 基带 (BB) 影像与 TRF3720 电压控制振荡器 (VCO) 及本地振荡器 (LO) 的混合产生了这些寄生信号。整合 BB 滤波器可最大限度地消除这些寄生信号。 本文将探讨这些寄生信号是如何出现在调制器输出端的。 图 1:OIP3 测量频谱分析仪截图 在图 1 所示的频谱分析仪截图中,有

- 关键字:

DAC 调制器

- 当我们在专门研究模数转换器 (ADC)、运算放大器 (Op Amp)、数模转换器 (DAC) 以及其他电子架构的工程类院校修完其主干课程以后,您可能会认为您已理解了这些电路的所有基本功能。大多数人均对 ADC 的工作原理有了一个很好的了解,但是对 DAC 的工作原理却不太熟悉,它究竟有何功能呢?同样,对于大多数人来说,DAC 只不过是一个输入端为数字信号数据而输出端为模拟信号数据的“黑匣子”。只有为数不

- 关键字:

R2R DAC

- 产品说明书的用途通常就是说明器件与理想模型的差异。例如,如果半导体供应商能够设计并制造出完美的、理想运算放大器,我们就不需要运算放大器产品说明书了,因为每个人都知道它们的特定属性(无限开环增益、无限输入阻抗等)。问题是没有这么简单。

首先简单介绍一下理想数模转换器 (DAC) 的属性,然后再深入讨论更为复杂的规范。下图是理想 DAC 的传递函数,重点列出了我们将要讨论的参数。

无论是 DAC 还是模数转换器 (ADC),任何数据转换器的最基本属性都是其分辨率。对

- 关键字:

DAC 运算放大器

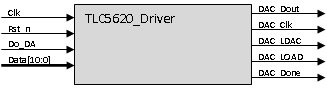

- 本实验中,我们使用FPGA来驱动了一片DAC芯片TLC5620,该芯片的特性如下所示:

TLC5620特性:

4路8位电压输出;

单电源5V供电;

串行接口;

参考电压输入高阻;

可编程的1次或2次输出范围;

同时更新的能力;

内部自带上电复位功能;

低功耗;

半缓冲输出。

小梅哥设计的该芯片的驱动模块的接口如下所示:

各个端口定义如下:

以下是代码片段:

input Clk;

inp

- 关键字:

FPGA DAC

mux-dac介绍

您好,目前还没有人创建词条mux-dac!

欢迎您创建该词条,阐述对mux-dac的理解,并与今后在此搜索mux-dac的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473