m0 文章 最新资讯

Microchip扩大耐辐射单片机产品线,为航空航天和防御市场推出基于Arm Cortex-M0+ 的32位单片机SAMD21RT

- 太空探索正迎来复苏期,一系列令人兴奋的新任务相继展开,如备受期待的Artemis II(阿尔忒弥斯二号计划)、JAXA SLIM 和 Chandaaryan-3成功登月以及New Space在近地轨道 (LEO)进行新部署。设计人员需要符合严格的辐射和可靠性标准的电子元件,以满足在恶劣太空环境中工作的要求。Microchip Technology(微芯科技公司)宣布推出新款耐辐射32位单片机SAMD21RT。该产品基于耐辐射(RT)Arm® Cortex®-M0+技术,采用64引脚陶瓷和塑料封装,具备12

- 关键字: Microchip 耐辐射单片机 航空航天 Cortex-M0+ 32位单片机

Arm Cortex-M0+ MCU如何优化通用处理、传感和控制

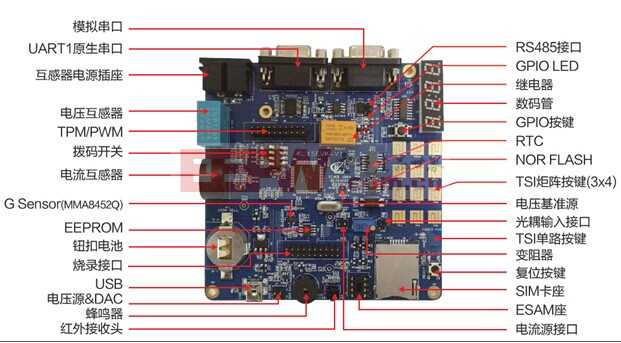

- 嵌入式系统中的微控制器 (MCU) 像是繁忙机场的空中交通管制系统。MCU 可以感知所在的工作环境,根据感知结果采取相应操作,并与相关系统进行通信。MCU 可以管理和控制从数字温度计到烟雾探测器,再到暖通空调电机等几乎各种电子设备中的信号。为了确保系统的经济性和使用寿命,嵌入式设计人员在设计过程中需要更大的灵活性。如果采用目前市面上的 MCU 产品系列,设计人员在当前和未来设计中可以重复使用的硬件和代码数量将很有限,并且计算、集成模拟和封装选项也很有限。这种有限的灵活性通常意味着设计人员必须向多家制造商采

- 关键字: Cortex-M0+ MCU

带有Cortex-M0+和MSP430基因,TI的MSPM0能否成功挤入MCU赛道?

- 2023年3月16日,上海,德州仪器 (TI)宣布推出可扩展的 Arm® Cortex®-M0+ 微控制器 (MCU) 产品系列,命名为MSPM0系列。TI称已推出数十款产品,还计划于今年推出100多款MCU。 TI中国区技术支持总监师英在发布会上说,请大家记住该系列的名字:MSPM0。的确,这是一个很特别的名字,和TI经典的超低功耗MSP430单片机(MCU)有些像。不过,Cortex-M0+也是arm公司主打超低功耗、高性能MCU的IP,与MSP430、TI的C2000市场可能有重叠?而且C

- 关键字: 德州仪器 MSPM0 MCU Cortex-M0+ MSP430

德州仪器发布全新Arm Cortex-M0+ MCU产品系列,让嵌入式系统更经济实惠

- 德州仪器 (TI)近日推出可扩展的 Arm® Cortex®-M0+ 微控制器 (MCU) 产品系列,进一步扩大德州仪器广泛的模拟和嵌入式处理半导体产品组合。该产品系列具有丰富的计算、引脚排列、存储器和集成模拟选项。此次发布的数十款MCU由直观软件和设计工具提供支持,使得MSPM0 MCU产品系列可助力设计人员将更多时间用于创新,减少评估和编程时间,将设计时间从几个月缩短至几天。Arm® Cortex®-M0+ MCU经济实惠、易于编程,可帮助简化电子设计。德州仪器MSP微控制器业务部副总裁 Vinay

- 关键字: 德州仪器 Cortex-M0+ MCU 嵌入式系统

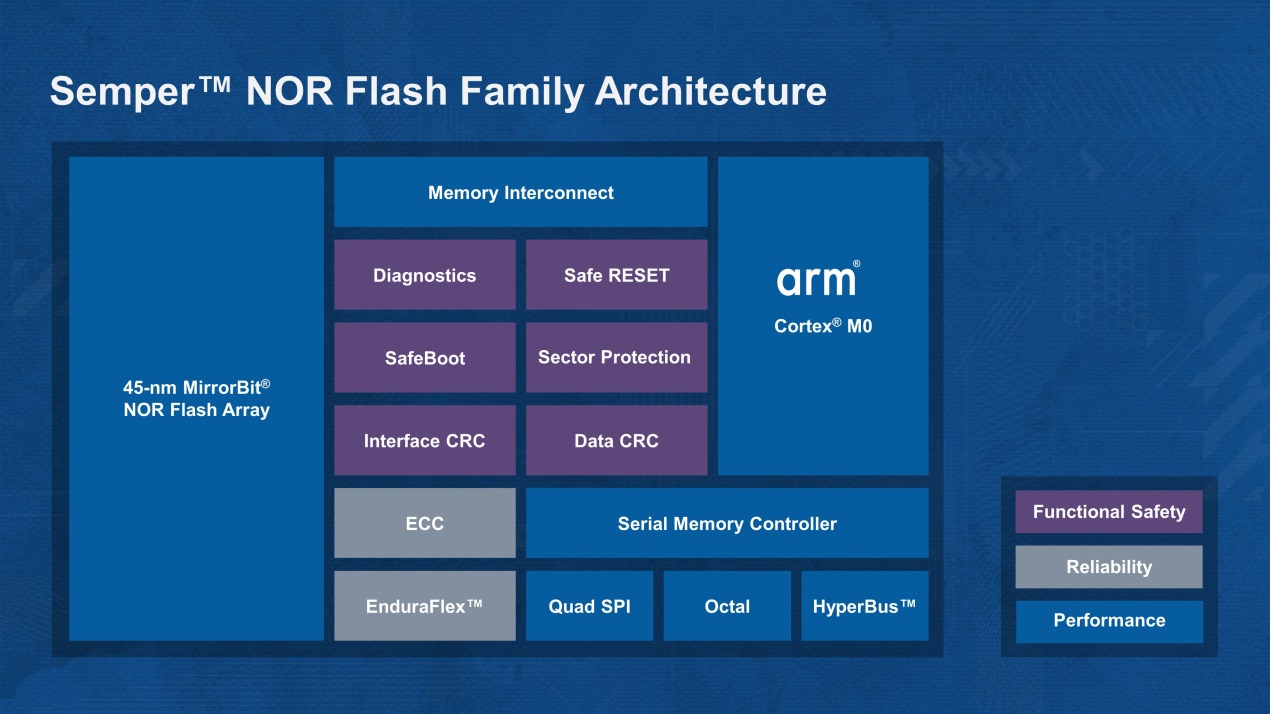

Denso为下一代汽车选用赛普拉斯Semper无故障存储器

- 北京,2019年4月10日 —— 全球领先的嵌入式解决方案供应商赛普拉斯半导体公司(Cypress Semiconductor Corp.)(纳斯达克代码:CY)日前宣布,赛普拉斯的Semper无故障存储器已被全球汽车零部件供应商Denso(电装)公司选中,支持其具备高级图形处理能力的下一代数字汽车驾驶舱的应用。Semper系列存储器采用了Arm® Cortex®-M0嵌入式处理内核架构,专为最严苛的汽车环境而设计。电装亟需具备高密度、耐久性且符合功能安全性标准的高性能代码与图形存储解决方案。赛普拉斯赛普

- 关键字: 赛普拉斯半导体 Semper无故障存储器 Arm® Cortex®-M0

m0介绍

您好,目前还没有人创建词条m0!

欢迎您创建该词条,阐述对m0的理解,并与今后在此搜索m0的朋友们分享。 创建词条

欢迎您创建该词条,阐述对m0的理解,并与今后在此搜索m0的朋友们分享。 创建词条