● Calibre 3DThermal 可为 3D IC 提供完整的芯片和封装内部热分析,帮助应对从芯片设计和 3D 组装的早期探索到项目 Signoff 过程中的设计与验证挑战● 新软件集成了西门子先进的设计工具,能够在整个设计流程中捕捉和分析热数据西门子数字化工业软件近日宣布推出 Calibre® 3DThermal 软件,可针对 3D

关键字:

西门子 Calibre 3DThermal 3D IC

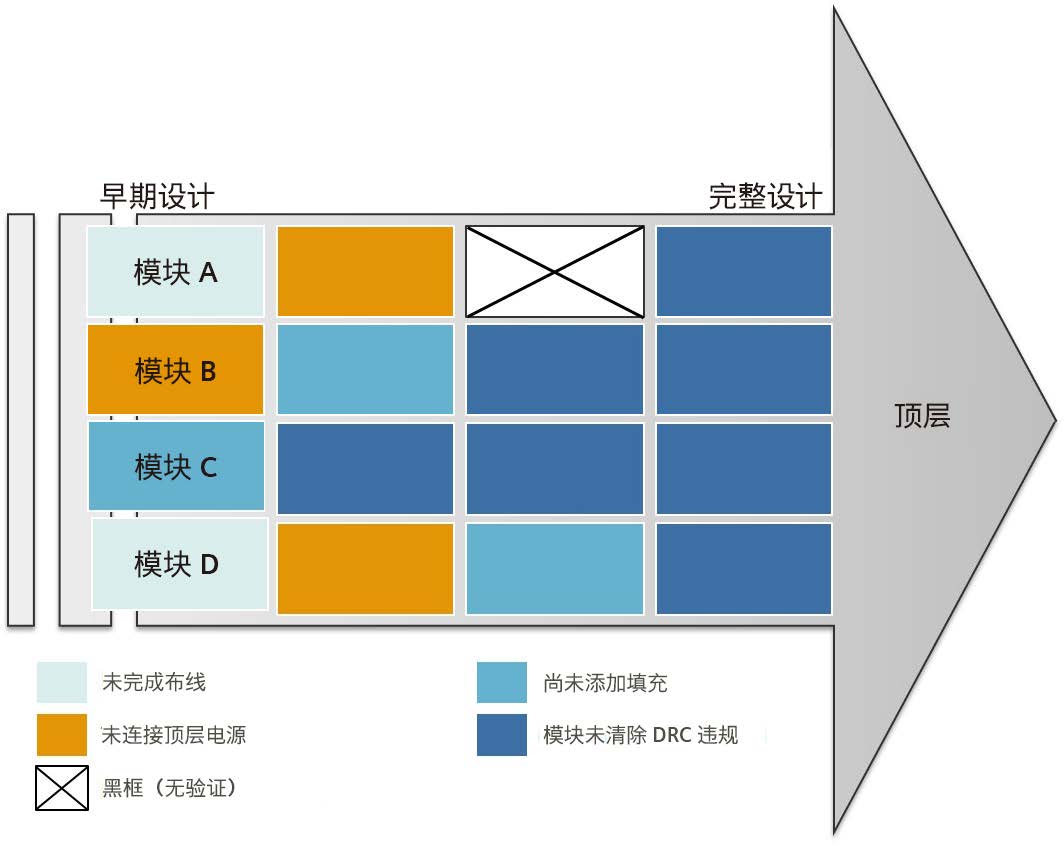

西门子数字化工业软件日前推出创新的 Calibre® DesignEnhancer 软件,可以让集成电路 (IC)、布局布线 (P&R) 和全定制设计团队在 IC 设计和验证过程的早期,进行自动化“Calibre 设计即正确”的版图修改优化,进而大幅地提高生产率、提升设计质量并缩短上市时间。Calibre DesignEnhancer 是西门子 Calibre® nmPlatform 物理验证平台一系列“左移”工具的最新成果,能够赋能定制和数字设计团队快速、准确地优化其设计,以减少或消

关键字:

西门子 Calibre DesignEnhancer Calibre 设计即正确 版图优化

西门子数字化工业软件近日为其集成电路 (IC) 物理验证平台 —— Calibre® 扩展一系列电子设计自动化 (EDA) 早期设计验证功能,可将物理和电路验证任务“左移”, 在设计和验证流程的早期阶段即能识别、分析并解决复杂的 IC 和芯片级系统 (SoC) 物理验证问题,进而帮助 IC 设计团队和公司加快流片速度。 在设计周期内更早地识别和解决问题,不仅有助于压缩整个验证周期,而且还能创造更多的时间和机会来提高最终的设计质量。西门子使用认证的签核 (signoff) 标准,为早期阶段的分析、验证和优化

关键字:

西门子 Calibre 设计验证

简介虽然产品可靠性一直以来都是半导体行业的一个重要因素,但随着交通运输、医疗设备和 通信等领域越来越多地使用电子设备,对于能够在设计的产品寿命期内按预期工作的集成 电路 (IC) 的需求已呈现出指数级增长趋势。然而,尽管对于精准的可靠性验证的需求已显 著增长,但使用现有的验证技术确保 IC 可靠性一直是 IC 设计公司面临的重大挑战之一。技 术节点尺寸的缩减加上不同类型的设计应用的快速增长,让该问题变得更加复杂,增加了 需要的可靠性检查数量及其复杂性。所有这些因素都在有力地推动对于准确的自动化芯片 可靠性

关键字:

EDA Mentor Calibre

背景1981 年是业界公认的电子设计自动化 (EDA) 商业化元年,Mentor, a Siemens business 自这一年开始,长期致力于深耕 EDA 工具领域。从一开始,我们的 Calibre® 验证平台就专注于为企业提供一流的验证流程。 在与全球设计人员、工程师和团队的日常互动中,我们一直在密切观察设计和验证周期,并不断努力改 进我们的工具以提高生产率。有一个趋势非常明显……流片变得越来越困难,需要的时间也越来越长。根据行业会议调查得出的统计 数据,每年至少有 50% 的预定流片出现延迟。这些

关键字:

EDA Mentor Calibre

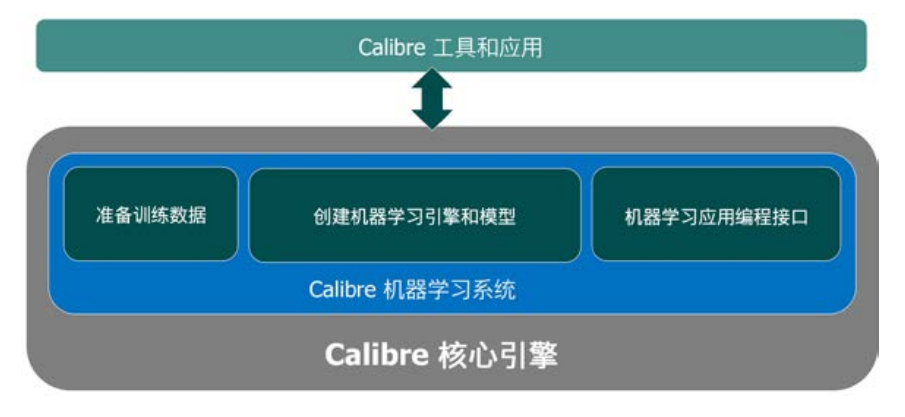

在20/22nm引入FinFET以后,先进工艺变得越来越复杂。在接下来的发展中,实现“每两年将晶体管数量增加一倍,性能也提升一倍”变得越来越困难。摩尔定律的发展遇到了瓶颈,先进制程前进的脚步开始放缓。但是由于当今先进电子设备仍需求先进工艺的支持,因此,还有一些晶圆厂还在致力于推动先进制程的继续发展。这些晶圆厂与EDA企业之间的合作,推动了先进制程的进步。从整体上看,当先进制程进入到14nm/7nm时代后,EDA工具的引入可以缩短研发周期,尤其是针对后端设计制造工具的更新,EDA起到了至关重要的作用。EDA

关键字:

机器学习 EDA Calibre

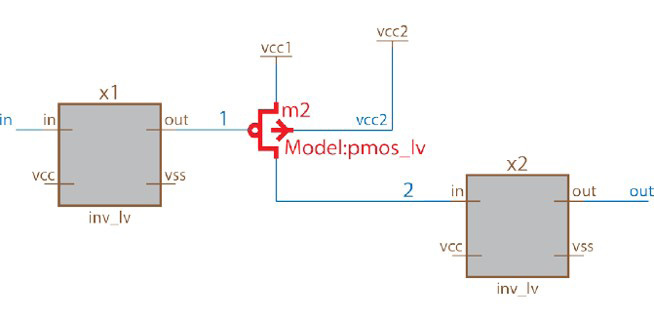

Mentor Graphics®公司(纳斯达克代码:MENT)今天宣布推出 Tanner Calibre One IC 验证套件,作为 Tanner™ 模拟/混合信号 (AMS) 物理设计环境不可或缺的一部分,使 Tanner EDA 的用户群可以轻松使用 Calibre® 验证工具的所有功能。该套件大大改善了 IC 设计和验证解决方案,使 Tanner 客户可以在更为集成的环境中使用 Calibre 物理和电路验证工具,尤其是在 Tanner L-Edit™

关键字:

Mentor Graphics Calibre

Mentor Graphics公司今天宣布,United Microelectronic Corporation (UMC) 正在为其客户开发一套新的IC 可靠性参考流程。这一全新的流程是基于Calibre® PERC™可靠性验证平台而开发,可检测细小的设计缺陷,如可能引起场内(in-field)故障的静电放电(ESD) 保护电路缺失,从而帮助客户提高其IC 产品的长期可靠性。此解决方案包括由 UMC 和 Mentor Graphics 正在联合开发的预先定义的检查,目标客户为采用

关键字:

UMC Calibre

Mentor Graphics 公司今天宣布推出全新 Calibre® xACT™ 寄生电路参数提取平台,该平台可满足包括 14nm FinFET 在内广泛的模拟和数字电路参数提取需求,同时最大限度地减少 IC 设计工程师的猜测和设置功夫。 Calibre xACT 平台可借由自动优化电路参数提取技术,针对客户特定的工艺节点、产品应用、设计尺寸大小及电路参数提取目标,实现精准度和周转时间 (TAT) 的最佳组合。 采用 Calibre xACT 平台进行电路寄生参数提取在满足最严格

关键字:

Mentor Graphics Calibre

明导国际(Mentor Graphics)日前宣布,联咏科技(Novatek Microelectronics)采用Calibre® xACT™ 3D提取工具来精准确认电路之寄生参数,以提升布局后(post-layout)芯片仿真的结果。

关键字:

明导 联咏 Calibre 场解算器

Mentor Graphics公司(纳斯达克代码:MENT)日前宣布,宏捷科技股份有限公司(AWSC)已经选择Calibre® nmDRC™和nmLVS™产品作为其针对手机和其他无线应用中砷化镓集成电路的金级核签物理验证解决方案。

关键字:

Mentor Calibre DRC

Mentor Graphics公司(Mentor Graphics Corporation)今日宣布,公司已对台积电Reference Flow 10.0中的工具和技术进行扩展。扩展的Mentor®流程支持复杂的集成电路高级功能验证、28nm 集成电路 netlist-to-GDSII实现、与无处不在的Calibre®物理验证和DFM平台更加紧密的集成和版图感知测试故障诊断工具。此外,新推出的Mentor流程还以Mentor工具解决功能验证、集成电路实现和集成电路测试中的低功耗设计问题

关键字:

Mentor Reference Flow Calibre Olympus-SoC TestKompress YieldAssist

calibre介绍

您好,目前还没有人创建词条calibre!

欢迎您创建该词条,阐述对calibre的理解,并与今后在此搜索calibre的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473