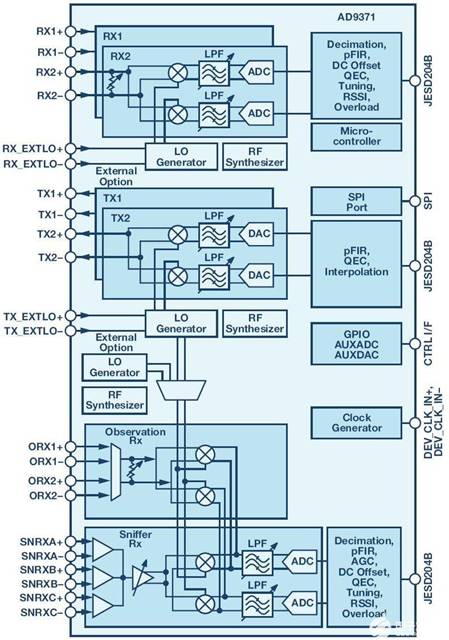

3G通信系统的直接调制无线电硬件结构(05-100)

本文引用地址:http://www.eepw.com.cn/article/91463.htm

图2 直接变频接收器结构

本振(LO)信号与输入RF信号的混频或泄漏耦合到RF输入,这可能在接收器中产生显著的dc 电压电平。对LO和RF之间进行最大隔离和通过谐波器,可使d c 偏移最小。在解调器I-Q通路中很好地匹配混频器和放大器的振幅和相位响应是关键性的。Si-BiCMOS解调器SKY73009的振幅和相位平衡可分别达到0~3dB和1U庵纸獾髌饕簿哂?0dB的LO和RF间隔离,这对于在接收器中保持低dc偏移信号是必不可少的。采用低性能解调器的系统将需要复杂和昂贵的dc定标技术。

采用开关LNA(前端接收器RFIC的一部分)和Si-BiCMOS解调器的DCR示于图3。采用这些关键性的器件,RF分析表明所得到的级联噪声指数为3.2dB ,级联增益为70dB。对于大多数3G基站实现(依赖于TTA噪声指数和缆线损耗)小于6dB的级联噪声指数是可接受的。所以,上面所建议的接收器结构,可提供1.9dB额外的系统余量。

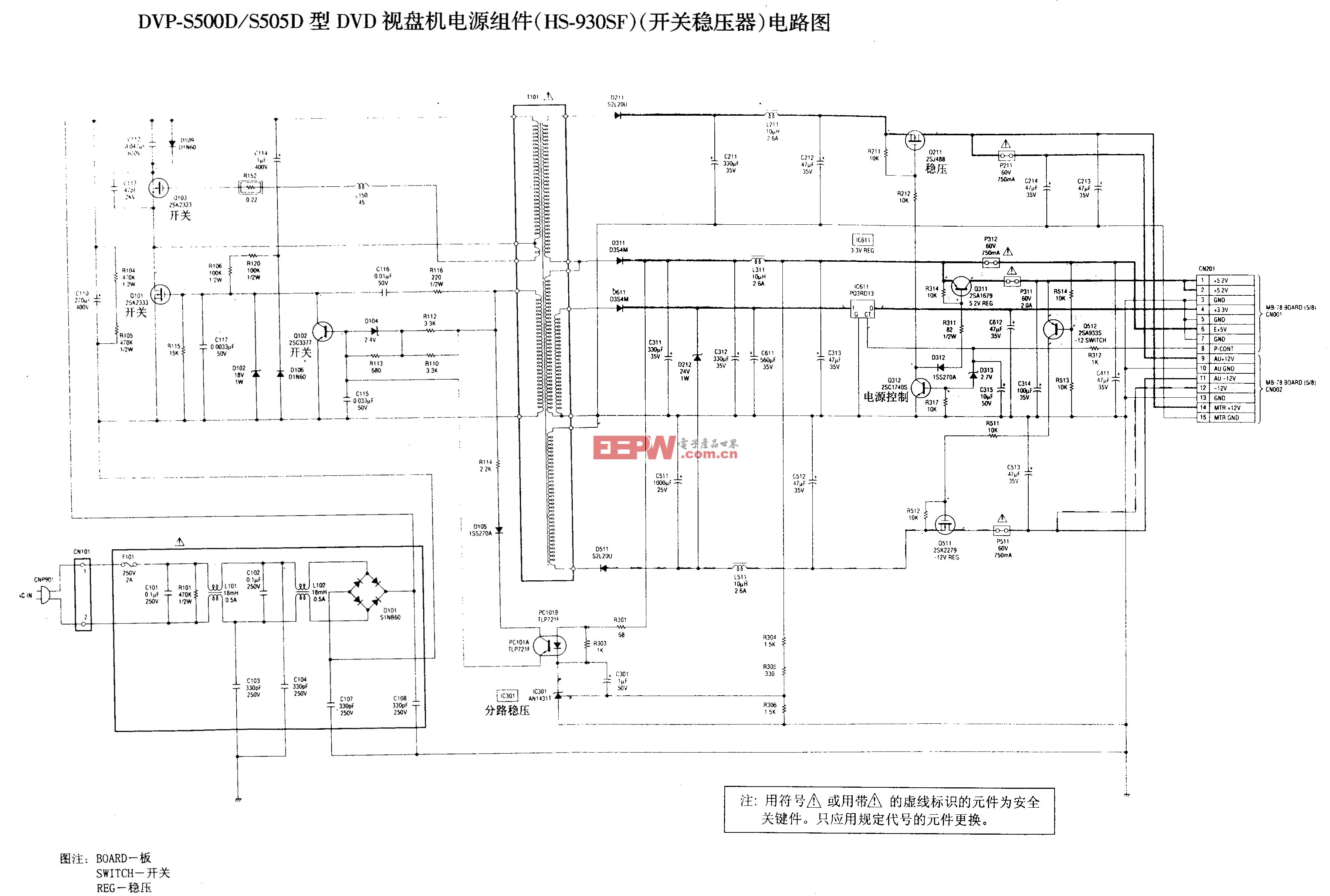

3G直接变频发送器

3GPP规范允许基端发送分集。用适当的统调(降低交叉耦合和增益加分路隔离)和定时同步,发送器分集可改善系统信噪比(SNR)和减轻多通路、信号衰减效应。然而,分集将增加系统实现成本、尺寸和功耗。采用低成本RFIC器件和直接变频结构,将有助于减轻这种负面效应对分集发送器的影响。

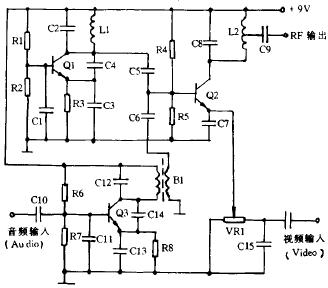

直接上变频发送器结构示于图4,这种结构正在成为更普遍的形式,这是因为这种结构具有元件数少,功耗低的特点。

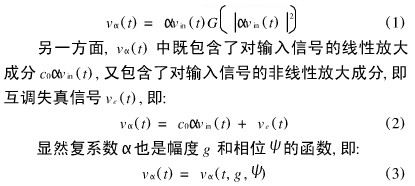

采用直接变频结构,DAC提供I-Q信号。来自DAC的I-Q信号可以是低通滤波的,这样可去除由DAC引起的混淆、谐波和寄生信号。然后,用直接正交调制器对滤波的I-Q信号进行直接调制和上变频到RF频率。调制器在I-Q分路之间必须具有适当的幅度和相位匹配,以使调制信号信息或误差向量幅度(EVM)的不纯最小。采用正交相移键控(QPSK)调制信号,WCDMA基站发送器所允许总的EVM是17.5%。系统工程师将分配大部分EVM系统预算给HPA(为了改善功率效率)。因此,希望来自调制器的EVM贡献要小或没有。所用的直接正交调制器的振幅和相位失调分别小于0.3dB和3o,而对EVM预算的贡献小于5%。

图4 直接变频发送器结构

图5 3G直接变频发送器的RF性能预算实例

从LO到RF端口的信号泄漏应最小,这是因为大部分直接变频系统中LO和RF输入信号是在相同的频率,而且,调制器之后的RF滤波,对于抑制任何的LO-RF泄漏将是无效的。现在,可以得到大于50dBc LO-RF隔离、大于60dBm 2阶输入截听点(IIP2)、小于-153dBm/Hz NF电平的直接正交调制器FRIC。这些RF性能值保证调制器对整个发送器链路的寄生发射不会有重大的影响。

可以电平控制上变频信号来补偿部件到部件、分集到主分路和温度增量变化。需要可变衰减来处理-10dBm~+10dBm(调制器的典型输出电平)输入功率电平,而不影响系统非线性。AA102-80可变衰减工作在大多数通用无线频带(0.5GHz~2.5GHz),它具有大于+45dBm输入3阶分量截听点(IP3)。可置的衰减范围大于30dBm(1dB步长)。

在电平控制之后,发送信号在馈入最后高功率放大器之前由线性驱动器放大。驱动器需要具有足够高的增益(一般20dBm~35dBm)和线性度以满足整个系统要求。用较高增益的驱放大器,可以减少高功率放大器所需的级数,使得成本降低和效率提高。可以得到大于25dBm RF增益和大于+40dBm输出3阶截听点(OIP3)的高性能线性驱动器。

WCDMA发送器的关键要求是邻信道泄漏功率比(ACLR)。3G规范要求ACLR1(1个信道或5MHz频率偏移)小于-45dBc,ACLR2(两个信道或10MHz频率偏移)小于-50dBc。ACLR测量通常在限定的测试模式1(包括64个专用物理信道DPCH信号和128扩展因数)。64个DPCH信号的功率电平和定时随机分布来仿真实际的信号环境。3G规范文件中规定测试信号功率电平定时。必须仔细分配发送器链路不同非线性部分的ACLR预算。表1示出ACLR预算在主要发送器部分的分配实例。

3G发送信号在0.01%累积互补分布(CCD)点测量时,其峰值平均值比(PAR)超过10 dB。3G信号的高PAR值对功率放大器的线性度提出严格的要求。对于表1所列ACLR预算实例,例1、例2和例3中线性驱动器可分别提供22dBm、20.5dBm和11dBm输出功率。例3是最可取的配置,因为它对基带元件、调制器和驱动器PA配置严格的要求,并会降低来自这些部分的可用输出功率,进而对HPA提出更高的增益要求。图6示出发送器链路框图和电平实例,用它可使总ACLR1达到大于标准-45dBc性能指标,其线性输出功率为+41dBm。发送器ACLR1预算紧密地反映表1中例2的分配。■(益林)

评论