深入研究DDR电源(07-100)

总线信号以VTT电压为中心上下摆动。当总线信号电压超过比较器的阀值电压时,它将输出一个如图所示的反向电压。在这个系统中,比较器的阀值电压为电源所提供的VREF电压。

本文引用地址:http://www.eepw.com.cn/article/81733.htm由于在比较器中存在滞回现象,信号的图片将有一个时间偏移,如图所示。

因此,在VIHmin 和VIlmax之间,仍保持着先前的VTT状态。

VTT和VREF的电压跟踪

为了保持信号的目标特性,VTT和VREF必须跟踪VDDQ。它们必须控制在1/2 VDDQ的范围内。

当VTT和VREF的跟踪失效时,由于‘High ’和‘ Low ’的周期不同, 信号的目标特性将会恶化,从而引起定时漂移。

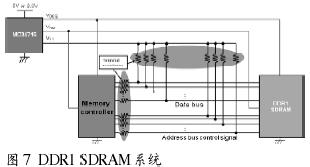

DDR1 SDRAM系统

在DDR1 SDRAM应用中,VTT被用来从电源IC中获取电压,以给数据总线和地址总线提供电源。

如图7所示,地址指令和控制线要求系统级端口接到一个等于1/2存储器电源电压(VDDQ)的电压(VTT)。在中点具有端电压,电源保证转换时间的对称。

VTT被用来从电源IC中获取电压,以给数据总线和地址总线提供电源。对于DDR1 SDRAM应用中的地址总线控制信号和数据总线信号都有端接电阻。需要一个没有任何的噪声或者电压变化的参考电压(VREF),用作DDR SDRAM输入接收器,VREF也等于1/2 VDDQ。VREF的变化将会影响存储器的设置和保持时间。

为了符合DDR的要求并保证最优的性能,VTT和VREF需要在电压、温度和噪声容限上进行严密的控制以便跟踪1/2 VDDQ。

DDR2 SDRAM系统

我们将会看到两个特别的例子,说明对于一个典型的DDR2系统,DDR总线如何连接。在下面描述的第一个存储器应用示例中。用于数据总线的VTT由VDDQ在存储器内通过ODT来生成。然而,有必要从电源IC中提供VTT来给地址总线控制信号。

注意:对于DDR2存储器,内置有数据总线的端接电阻,但是在DDR1存储器的应用中,仍需要用于地址总线控制信号的端接电阻。

现在,让我们来看一种特殊情况,其中DDR2存储器的应用连接不需要VTT电源和端电阻,在这种情况下,当控制器和存储器之间的地址总线控制信号的导线长度足够短的情况(如小于63.5mm);VTT的电源和端接电组是多余的。

存储器相关文章:存储器原理

评论