在需求多路高分辨率ADC的应用中实现前所未有的成本和性能

很久以来,对于许多科学、工业、医疗和消费领域的应用中的关键系统的实现来说,模数转换器都是最关键的器件。随着对功能集和性能双方面需求的持续增长,设计师不断地追求更具成本效益的方法使数据转换电路实现所期望的性能指标。

本文引用地址:http://www.eepw.com.cn/article/78339.htm为了满足应用目标,覆盖范围极广的复杂设计,例如自动测试设备(ATE),医疗仪器和监控设备,数据采集系统,实验室仪器以及工业自动化方面所用的可编程逻辑控制器(PLC)等,都取决于高分辨率的ADC。其结果是,ADC为现实的“模拟世界”和利用数字信息的“处理世界”之间提供了一座桥梁。

对于ADC的基本需求始终都离不开分辨率、精度和带宽。在选择ADC时,其他还必须要考虑的是信噪比性能、失真和延迟。在许多应用中,为了处理高频或连续读取各种传感器的数值,需要ADC具有快速响应。在ADC内部能够有效地处理多路信号的能力也正变得日益重要。这是因为在一个器件里处理多路模拟信号的需求正日益增加,例如在设计PLC时 ,要求能够在监控的同时,还能够整合同一生产环境下的多种传感器的实时输入。

许多传统ADC的输入端较难驱动,因而需要增加成本合适且具有高性能的输入缓冲器,以便提供连续处理场景中所需的响应。另外,某些ADC架构中甚至强行增加了“强制性静止时间”,即在采样时间内系统不能访问ADC,这更增加了设计的复杂度。

当然,在任何器件的选择中都必须考虑的其他要求还包括器件自身成本以及在整个设计中为确保合适的功能所需的辅助电路的成本。这一点对于ADC来说更为重要,特别是用在高性能的多元环境中的ADC,这是因为由于所选得ADC的类型不同,所需的辅助电路的相差很大。例如,如果ADC自身不能提供优异的噪声抑制和测量精度,就需要精心设计整个电路才能满足性能目标。在这方面,基于传统的连续逼近寄存器(SAR)型ADC的设计还对电路板空间,成本和功率方面提出特殊的挑战,因为需要设计很容易超过SAR型ADC自身的低功耗指标的输入缓冲器。所有这些因素在设计目标的成本效益方面都起着重要作用。

传统的SAR方案

传统上,上述的各种高性能应用都采用SAR架构的ADC,这种ADC能够提供连续时间点上的一系列快速取样。SAR型ADC通常瞄准的是需要快速响应和低延迟的应用,但是,SAR型ADC对噪声比较敏感,动态非线性(DNL)性能相对较低,通常需要大量的辅助电路,从而增加了采用SAR型ADC的设计总成本和复杂度。

线性度较差也带来一些具有特定的挑战性问题,因为该误差无法利用信号的过采样来平滑。在非常多的情况下,设计师必须通过过度要求SAR型ADC的指标以及设计复杂的系统来弥补SAR型的DNL性能。类似地,SAR型较高的噪声灵敏度和有限的噪声抑制能力也为设计带来一些额外的挑战,特别是在许多台设备共同部署的噪声比较大的环境里,例如生产车间里的一系列PLC以及彼此相邻的许多医疗仪器设备。

相比较,采用Delta-Sigma架构的ADC能够提供较好的DNL和噪声性能,并且很少需要复杂的辅助电路。以前,没有人考虑过在要求低延迟、高变换速率以及实现高信号带宽的高性能应用中使用Delta-Sigma ADC。不过,根据本文图中所示的测试数据,这种传统的观念已经不再适用。

新型高吞吐率Delta-Sigma架构

随着高吞吐率的CS556x/7x/8x家族的数据转换器的推出,Cirrus Logic大大扩大了设计师的选择范围。该系列包括16位和24位的ADC,采用了先进的高吞吐率的Delta Sigma架构,转换速率达到200ksps。相对于SAR架构,该架构的器件响应速度更快,延迟更低,因而成为传统上要求使用SAR型ADC的应用中更具成本效益的理想替代。

该产品家族中的所有产品都具备下列关键性能:

1. 带缓冲的高阻抗输入(单端或差分);

2. 5V 或 + 2.5V 模拟电源;

3. 1.8V、 2.5V 或3.3V 数字电源;

4. 全部带有自校准 (用于电源或温度变化时的偏移和增益误差校准);

5. 灵活的串行数字接口(主/从模式);

6. -40ºC 到 +85ºC的工作温度范围;

7. 24引脚的SSOP封装。

整个家族的所有器件的引脚兼容,因此设计师可以将验证过的设计平滑地移植到其他多种产品平台中,将重新设计减到最少。

单周期延迟

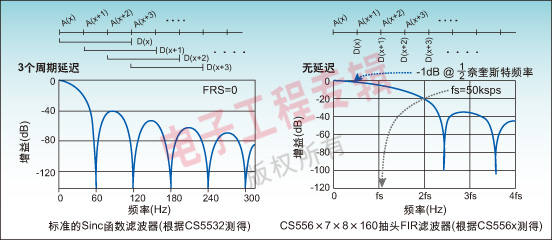

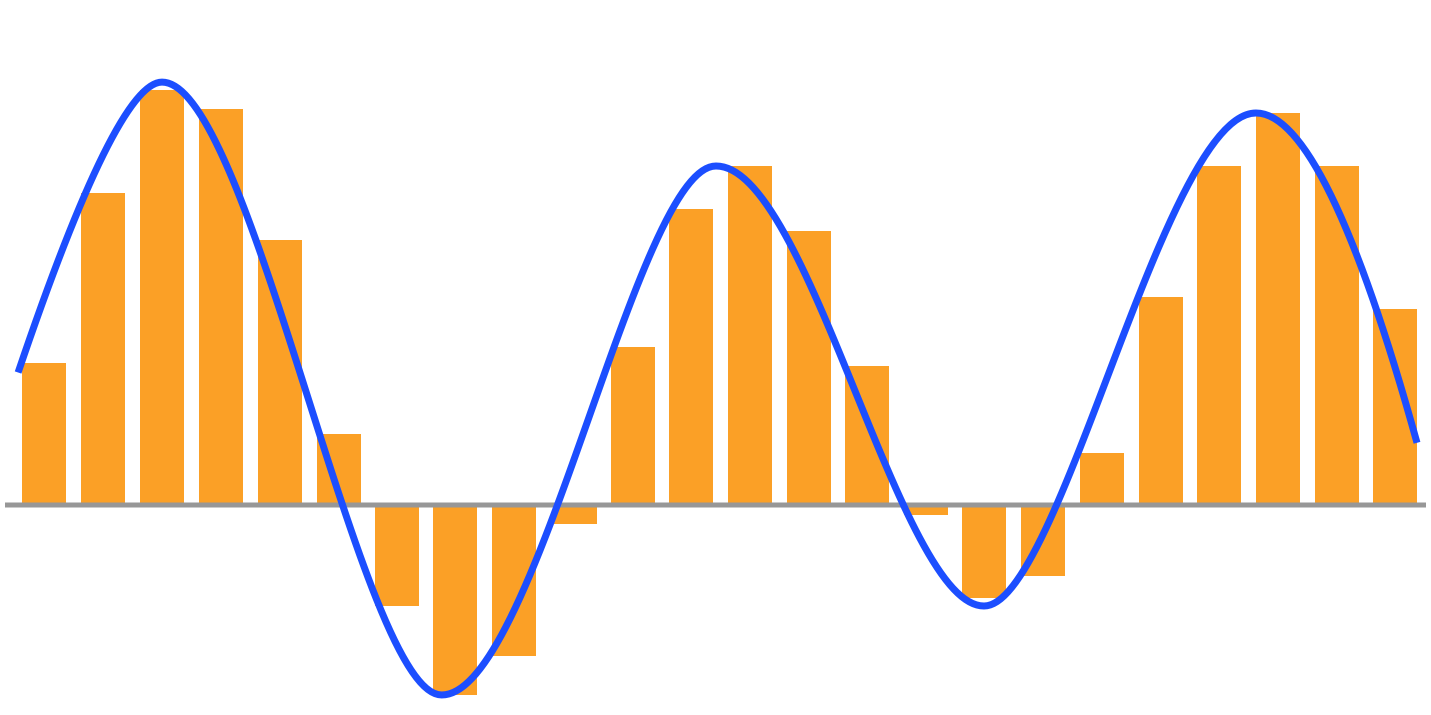

过去,Delta-Sigma型ADC主要用于如来自温度传感器和重量标准载荷单元的慢变化信号的最高分辨率测量。由于在嘈杂的数字环境中,噪声抑制性能是获得测量高精度的关键,设计师们已经习惯于采用长“sinc”函数型数字滤波器,这种滤波器对电源线上的干扰(如50和60Hz的电源工频及其谐波)具有优异的抑制能力。这些滤波器很容易设计,占用很少的芯片面积并具有很好的噪声性能。但是,这种滤波器响应太长(在提交输出字之前需要处理许多周期的输入信号),因此,对输入信号的变化响应很慢。例如,在图1的左侧,显示出在高分辨率家族中流行的CS533x家族器件所用的数字滤波器的转换延迟高达3个周期。

CS556x/7x/8x家族器件采用了非常快的FIR滤波器,这种滤波器具有两大优点。首先,该滤波器对两倍的采样频率的响应几乎是平坦的,为用户提供了无限的频率响应,这正是采用SAR型转换器所期望的。其次(如图1中的右侧所示),这种滤波器处理很快,只需要一个采样周期就可以提供输出字。这种单周期转换延迟使得这类新器件能够提供delta-sigma型ADC的卓越的噪声和DNL性能,又能提供SAR型转换器的高采样率和Nyquist带宽。

图1:Delta-Sigma ADC与SAR型ADC延迟性能的比较。

这类新器件的另一个关键优点是克服了许多传统的SAR型器件所强加的“静止期”,这种静止期指的是在采样处理的部分时间内不能读取转换器的输出。CS556x/7x/8x的测试结果显示,在转换期间的任何时刻,都可以读取数字输出,因而不影响器件的性能,包括全速工作期间。

另一个重要的功能是能够按需转换(SAR型转换器的另一特点)。该功能使得这类器件非常适用于管理生产环境中经常需要的异步测量。该能力允许将转换与特定事件相协调,例如带多个脉冲或其他传感器输入的 同步流。此外,利用双电源可以实现真正的双极输入。目前业界的产品都是使用单电源(只有+5V),因此需要用一个电平移位器将双极信号移到地电平之上,这样就会产生额外的增益和偏置误差,从而增加系统误差。

缓冲输入具有许多优点

如上所述,SAR型转换器提出了许多设计挑战。在模拟输入端最为明显,在这里设计师必须密切注意元器件的选择和电路布局,以便在面对多个噪声源的环境里获得转换器的测量精度。因为在SAR架构里采用了高速比较器,加上器件内部的快速变换数字电路的影响,SAR转换器自身就是主要的噪声产生器,通常这对许多设计师-即便是最富经验的设计师来说,都是没有办法和令人头疼的事情!

比较起来,Delta-Sigma转换器具有许多固有的优点,包括对噪声的低灵敏度,以及固有的高精度,从而使性能得到大量的改进。首先,这类器件集成有高阻输入缓冲放大器,从而在无需复杂和成本高昂的外部输入缓冲电路的条件下,很容易地实现高性能指标。SAR型器件在转换期间,通常利用某种类型的采样保持电路来维持输入信号采样的稳定。结果,这些器件的输入端对信号源的阻抗非常低,还有一个很大的电容,故需要一个非常可靠的放大电路来维持ADC的输入电平在动态采样期间保持稳定。这可能是一项挑战性极强的设计任务,因为在许多情况下,需要一个成本和复杂度超过转换电路中所有其他部分的缓冲电路,因为使采样输入信号性能降低的噪声将直接影响转换精度。换句话说,在某些应用中,这类新型的高吞吐率的Delta-Sigma型转换器件,有时可以直接由传感器驱动,不需要传统SAR型转换器重所必需的缓冲放大器。

其次,由于对输入过采得到多个样本(在采样率为8MHz时,对于24位的CS5560/1器件来说是160个),Delta-Sigma调节环路内部提供的低通滤波器和数字滤波器中所实现的算术平均,抑制了甚至就根本不受大部分噪声的影响,而这些噪声在基于SAR型转换的设计中则会产生很大的问题。

目前,在混合信号环境中经常遇到的另一个约束是,由于利用低电压亚微米CMOS工艺所造成的单电源工作模式。新型的CS556x/7x/8x家族的器件在使用最低±2.5V的双电源时,能够提供真正的双极模拟输入。这对测量参考电平为地电平的交流信号或具有负输出的变频器的用户来说,是一个极大的优点,因为为了满足单电源转换器的输入要求,需要一个电路将信号偏移到地电平以下,该电路需要一个电平移位放大器,而该放大器也会为敏感的小信号引入额外的噪声和偏移误差。

下面将提供关键参数的详细比较,例如失真性能和动态非线性。

失真性能

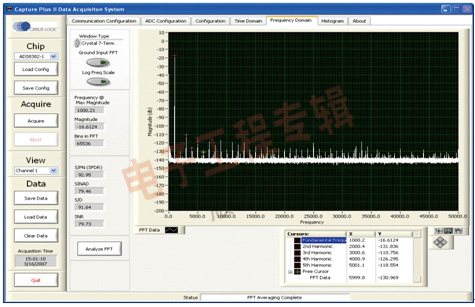

图2a和2b给出了常用的SAR器件和高吞吐率的Delta-Sigma CS5571器件的失真性能的详细比较。可以看到,CS5571的性能远胜过SAR器件。在FS的-12dB处,SAR的信号失真比为91.6dB,而CS5571的S/D比值为100dB。Delta-Sigma 型转换器具有较好的失真性能的一个主要原因是具有优异的代码尺寸的一致性,这是因为具有比SAR型转换器好得多的DNL性能的结果(详见下节)。

图2a SAR FFT Distortion @ -12 dB of FS

图2b – CS5571 FFT Noise Distortion @ -12 dB of FS

动态非线性性能

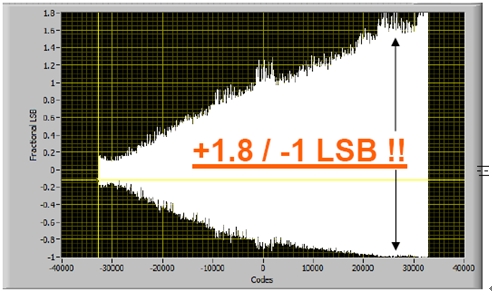

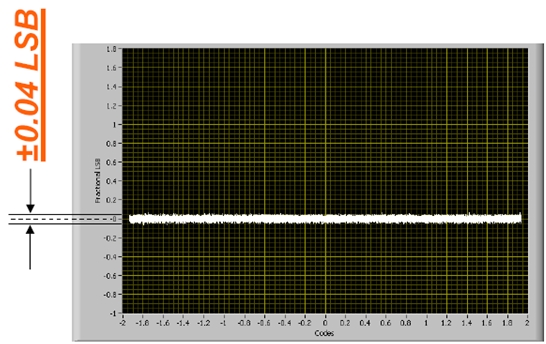

DNL基本上是归一化到满刻度的代码宽度变化的量度。它实际上就是偏离统一的或平均代码值的值,导致一个代表与另一个代码值不同的电压步进量。图3a和3b所示的DNL,对代码值的变化提供了一个直观的显示,该变化将增加码丢失,获取和偏移误差。正如所见,根据竞争对手领先的SAR型器件所测出的DNL曲线,代码值变化很大,而在转换速度相同的条件下, CS5571的DNL在整个的输入范围内,误差都非常低。

图3a – 16-bit SAR DNL Plot (In fraction of lsb)

图3b – 16-bit CS5571 DNL Plot (In fraction of lsb)

优异设计源于悠久历史

还需要着重指出的是,这个新家族的高吞吐率Delta-Sigma器件,来自一个已被世界各地普遍认可的供货商,该公司具有消费品和工业市场上范围很广的高精度模拟和混合集成电路的研发经验。Cirrus Logic广泛的产品线已经包括许多用于消费领域,专业和汽车娱乐应用的模拟和混合音品IC,以及许多工业应用,如工业测量,分析仪器,消费品,数字功率计和地震测量系统中的高精度模拟和混合IC。

我们的历史可以追溯到1984年(当时的Crystal Semiconductor),之所以能够研发出来CS556x/7x/8x家族的器件,是因为具有研发领先IC的久远历史以及信奉充分理解终端应用和不断瞄准新的产品研发来解决现实世界的挑战。作为一个长期的、在SAR和Delta-Sigma ADC方面极具经验的供货商,Cirrus Logic公司的理念是不断提升经验和研发能力,来克服各种产品的缺点并研发两方面都最好的新产品。

典型的应用场合

高分辨率再加上不受限的信号带宽,使得设计师能够实现满足其特定应用需求的噪声处理和信号滤波。在使用的地方,这甚至可以包括自适应滤波,即系统可以动态地调整滤波器来适合变化的环境,从而提供以前根本无法提供的新能力,以满足高分辨率测量应用。

受益于该项新技术的最激动人心的应用领域之一就是用于PLC和处理控制系统的嵌入式设计。最近几年,工业自动化环境演进到更侧重于分散控制,采用密集的多功能解决方案,这种方案可以处理各种实时的传感器输入,还有嵌入式智能以及实现本地决策环路的闭环响应。许多情况下,较差的DNL性能和噪声特性,以及对额外的辅助电路的需求,限制了SAR在实现新一代的模块PLC方面的应用。

该高吞吐率Delta-Sigma器件的推出解决了这些障碍,使得PLC设计师能够实现高分辨率和低延迟,与此同时,还保持高测量精度,并具有非常一致的DNL性能。这一点对于实时闭环应用尤为重要,因为这种应用中重要的是不能丢失代码并避免ADC的传递函数发生阶跃,否则将会导致控制环路出现“不确定”条件。

自动测试设备是另一个关键的应用领域,在这种应用中,需要对多路同时输入的输入流进行监控和实时处理。因此,要实现精确的测试结果,一致的DNL性能是至关重要的,特别是在一个较长的观测时间内连续地监控比较小且有时有一些细微变化的测试信号。

此外,对于用来测试和测量对噪声敏感的设备的某些ATE系统,实际上SAR型转换器的固有噪声灵敏度是一个另外的挑战,因为它会干扰测试结果。如上所述,设计师通常选用分辨率和速度比实际需要高得多的SAR型转换器,然后平均多个样本来获得所期望的系统测量精度。而采用这种新型的高吞吐率的转换器,每一次读取都可以得到足够的精度,因此可以彻底不需要过高的分辨率或采样率和后处理。在ATE领域,这将产生很高的吞吐率,这对终端用户来说等同于降低测试成本。ATE应用还代表着另一个应用领域,在该领域中,自适应滤波通过在测试过程中动态调节测试参数,可以提供一些令人更感兴趣的优势。

医疗设备是另一个从这种新型的高吞吐率数据转换器受益的重要市场分支。这些设备包括病床旁边的监控器,血压分析仪,以及其他类型的诊断系统,这些设备和系统通常对使用12-16位的ADC,不过设计师们已经意识到了转用更高分辨率的ADC的潜在好处了。这将能使他们对传感器信号直接数字化,然后利用软件对信号进行信号获取和误差校正,从而可以改进设备的精度和分析的灵活性。这些新型的高吞吐率的Delta-Sigma器件与原来的16位和24位的ADC引脚兼容,故设计师可以平滑过渡到更高的分辨率,无需冒很大的设计风险或牺牲未来的灵活性。

测重设备是另一个关键的应用领域,这里,高精度的连续测量对于实现精密的批控制和高速称重功能起着关键作用。实际上所称量的产品范围很广,从混凝土这类的笨重物品,到向土豆片这类的消费类产品。但要实现高质量和吞吐指标,高精度和快响应是关键。例如,用来称重土豆片的设备必须能提供的精度高达大约0.01盎司,连续的称重速度达到每秒3~5包。

本文小结

由于该高吞吐率数据转换器家族的每一款都能提供前所未有的DNL性能,故设计师在应用目标的成本效益的实现方面有广泛的选择范围。实际上,由于该家族中的16位转换器可以提供出色的线性度和噪声性能,在许多情况下,用户可以选用速度比过去更低的ADC,而且无需对来自噪声性能较差的SAR器件的多个数据样本进行平均,这是因为这些新型的ADC利用一次变换即可提供无噪声干扰的足够高的显示精度。

这种先进的数据转换器架构方案满足了高分辨率,低延迟和高采样率等主要目标。能够支持需要连续采样的应用,既不需要较大的输入缓冲器和复杂的辅助电路,也不需要对器件的输出缓冲器的访问施加一些苛刻限制。

评论