FPGA系统设计的仿真验证之:SDRAM读写控制的实现与Modelsim仿真

(5)仿真。

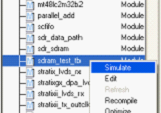

本文引用地址:http://www.eepw.com.cn/article/273721.htm在Workspace浏览器中选择“Library”复选页,单击Work左边的小加号。在弹出的子菜单里面找到仿真模块“sdram_test_tb”。双击或右键选择“Simulate”选项,ModelSim就会自动运行仿真,如图7.40所示。

图7.39 编译正确通过 图7.40 仿真

(6)观察波形。

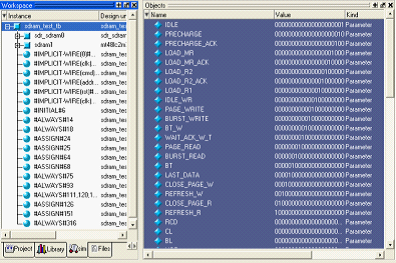

在Workspace浏览器中选择“Sim”复选页,可以看到仿真模块的实例列表,如图7.41所示。

图7.41 仿真模块实例列表

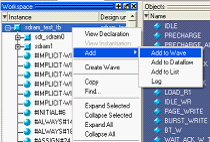

如图7.42所示,右键单击顶层测试模块,选择“Add”/“Add to Wave”选项,将该仿真模块的所有实例添加至波形观察器中。

添加后,ModelSim将会自动打开一个波形观察器,并将顶层测试模块的所有寄存器和接口添加进去。回到ModelSim的界面,在命令输入窗口中键入“run 20us”,开始执行仿真,如图7.43所示。

图7.42 添加实例至波形观察器 图7.43 执行仿真

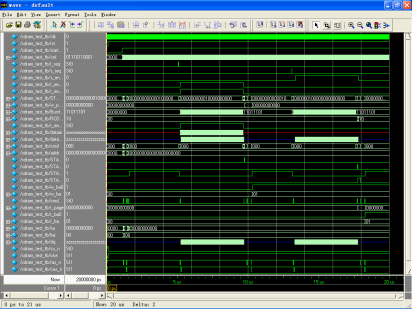

执行仿真后,经过相应的仿真时间,就可以在波形观察器中看见如图7.44所示的仿真结果。这个就是通过利用已有的SDRAM控制器及SDRAM器件模型,由用户编写对SDRAM控制器的状态机控制后得到的仿真结果。

图7.44 SDRAM控制器仿真结果

7.6.4 小结

本节对数字系统中常用的存储器SDRAM做了初步的介绍,并在Modelsim中实现了对SDRAM控制器的仿真。通过这个实例,读者能够掌握分立器件是如何与FPGA逻辑实现Modelsim联合仿真的。

在大型的系统设计中,在系统硬件实现前对系统进行仿真是非常必要的。而这个仿真又不仅仅局限在FPGA等可编程逻辑器件内部,与之相关的分立器件也是系统仿真的重要组成部分。因此掌握分立器件的联合仿真是一个非常重要的技能。

评论