基于FPGA的DDR3多端口读写存储管理系统设计

3 DDR3用户接口仲裁控制模块设计

本文引用地址:http://www.eepw.com.cn/article/271735.htm每片DDR3只有一组控制、地址和数据总线,因此同一时刻只能有一个设备在访问。常见的总线切换方式有两种:一种是轮询机制,软件实现简单,但实时性不高;一种是仲裁机制,设备发送中断请求,从而进行总线切换。由于视频图形显示系统对实时性要求高,因此选择仲裁机制。

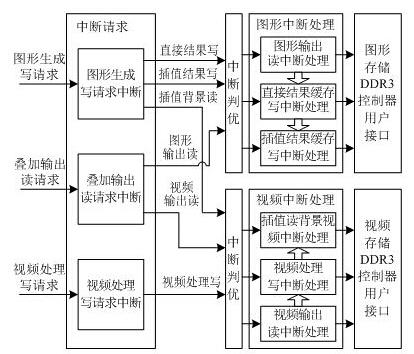

DDR3用户接口仲裁控制框图如图5所示。为了提高并行速度,将图形和视频分别进行中断处理。将设备中断请求解析成多个子请求,进行优先级判断,每个子请求对应一个中断处理逻辑。

图5 DDR3 用户接口仲裁控制设计框图

3.1视频处理写请求中断处理器设计

由于视频处理写请求不涉及到图形中断处理,所以对应一个子请求:视频处理写子请求。

视频处理模块将采集到的视频经过缩放、旋转等操作后存储在缓存区中,当缓存区满时发送视频处理模块写请求。视频处理写中断处理主要是从视频处理模块的缓存区中将地址和数据取出,写入到视频存储DDR3中。

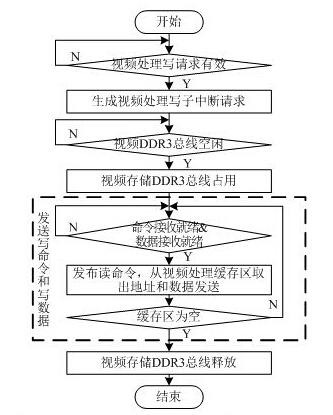

图6 视频处理写请求中断处理流程图

视频处理写请求中断处理流程图如图6所示。当视频处理模块写请求信号有效时,生成子中断请求信号,若总线空闲则响应该中断。当命令接收就绪(app_rdy=1)且数据接收就绪(app_wdf_rdy=1)时,从视频处理缓存区中读取地址和数据,同时发送写命令、写地址和写数据。若缓存区为空,说明全部写完,视频处理写中断结束。

3.2叠加输出读请求中断处理器设计

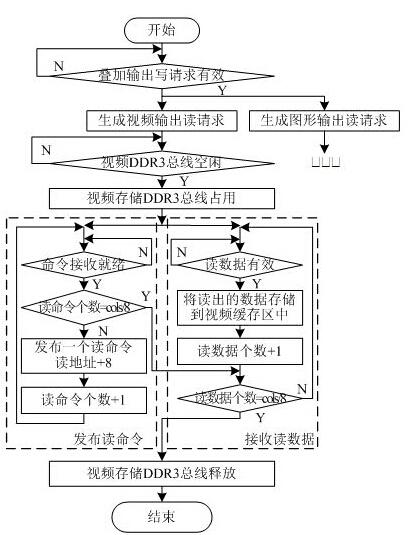

叠加输出模块需要从DDR3中将待输出的图形数据和视频数据存储到行缓存中,因此分为两个子请求:视频输出读请求和图形输出读请求。由于两者分别在图形中断处理和视频中断处理中完成,因此可以同时进行。

视频输出读中断处理主要从视频存储DDR3中读取1行视频数据写入到叠加输出模块的视频缓存区中,流程图如图7所示。本系统中突发长度为BL=8,即每个用户时钟周期对应接收同一行地址中相邻的8个存储单元的连续数据。输出视频分辨率为cols×rows,则地址系统需要发送cols/8个突发读命令。数据系统接收读数据时,若读数据有效(app_rd_data_valid=1),则将读到的数据存储到叠加输出模块的视频缓存区中,同时读数据个数加1.当读数据个数为cols/8时,所有读命令对应的读数据全部接收,视频输出读中断处理结束。

图8 视频输出读中断处理流程图

图形输出读中断处理包含两个步骤:从图形存储DDR3中读取1行图形数据写到叠加输出模块的图形缓存区中;将刚刚搬移数据到图形缓存区的DDR3存储空间清零。前者与视频输出读中断的处理过程类似。

图形数据写入DDR3时只写入有图形的位置,而不是全屏扫描,如果不进行清屏操作会导致下一帧图形画面上残留上一帧的图形数据。清屏操作指图形输出后将DDR3中对应地址的存储空间全部写入数值0,从而将当前图形数据清除。

3.3图形生成写请求中断处理器设计

图形生成是接收CPU的图形命令并进行光栅化,将结果先存储在直接结果缓存区和插值结果缓存区中,从而存入到DDR3中。当一帧图形全部绘制完成后发送图形生成模块写请求。图形生成写请求分为三个子请求:直接结果写中断请求、插值背景读中断请求、插值结果写中断请求。

fpga相关文章:fpga是什么

存储器相关文章:存储器原理

评论