噪声频谱密度——一项“新”的ADC指标

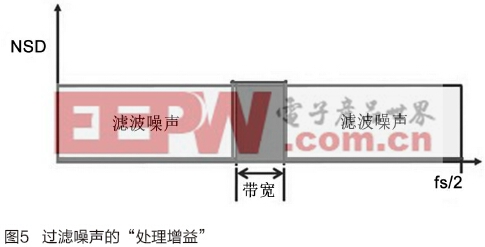

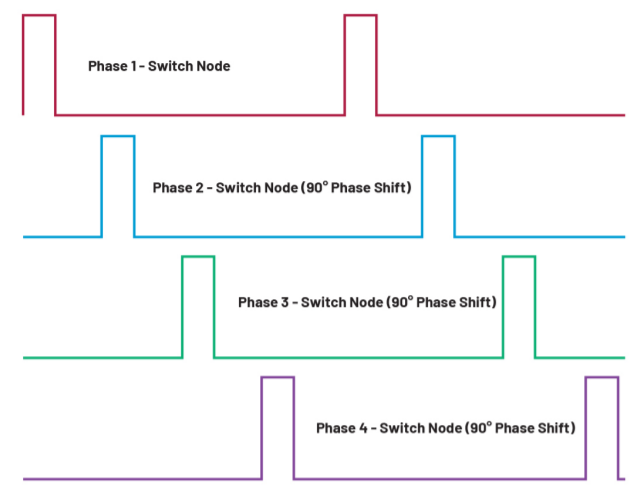

在一些应用中,主要目标信号仅位于很小的带宽(BW)内,比奈奎斯特带宽小很多。 这时,可使用数字滤波器来滤除较小带宽之外的噪声。 此过程实现方式为,在从奈奎斯特速率ADC输出数据前,使用数字下变频级来抽取、调谐和过滤数据。 这时,我们的SNR计算必须包含此滤波过程的校正系数,该系数就是过滤噪声的“处理增益”(图5)。

理想SNR(含处理增益)= 6.02*N + 1.76 dB + 10log10(Fs/(2*BW))

假设我们使用的是采样频率为100 MSPS的奈奎斯特速率ADC,但是,我们的系统应用不需要观察转换器的整个50 MHz奈奎斯特带宽。 相反,我们仅希望观察奈奎斯特带宽中较小的八分之一部分,即20 MHz和26.25 MHz之间的6.25 MHz带宽部分。 如果我们实施数字滤波算法并将滤波器调谐到此目标带宽,可以计算得到因过采样而产生的+9 dB处理增益:

处理增益 = 10log10(Fs/(2*BW)) = 10log10(100*106/(2*6.25*106)) = 10log10(8) = 9 dB

带宽每减少2次幂,因过滤噪声而产生的处理增益就会增加+3 dB。 这可从上例中看出,带宽减少(1⁄2)3会产生3 x 3 dB的处理增益。

还有哪些配套元件可影响系统中ADC的NSD性能?

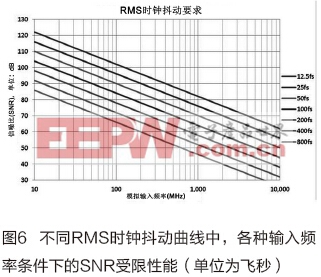

许多外部因素都可导致高速ADC的最佳性能下降。 这会造成SNR下降而有效噪声密度升高。 任何影响ADC的SNRFS或采样速率的补充元件都有可能影响系统中ADC的NSD。 让我们来重点看看时钟抖动,这是造成ADC在高采样频率时SNR性能下降的常见元凶之一。

高速、高分辨率ADC对时钟输入信号的质量非常敏感。 要在高速ADC中实现出色的SNR性能,必须根据应用的输入频率要求,仔细考虑均方根(RMS)时钟抖动。 即便是在性能最高的ADC中,RMS时钟抖动也可能限制SNR,在较高输入频率时问题更为严重。 虽然这不会改变ADC的NSD潜在能力,但在具有高抖动时钟的系统中会限制其实际SNR性能。

使用相同的RMS时钟抖动时,ADC的模拟输入频率每翻三倍,最佳的SNR性能便会下降10 dB。 在给定的输入频率(fA)下,仅由孔径抖动(tJ)造成的信噪比(SNR)下降计算公式如下:

SNR = 20 × log10[1/(2 × π × fA × tJ)]

如图6所示, 随着输入频率增加,需要较低的RMS时钟抖动,才能实现较低输入频率下同样的SNR限制。 例如,200飞秒(fs)的RMS时钟抖动会将ADC的SNR性能限制为低于70 dB(250 MHz下)。 但是,1 GHz的输入信号需要50飞秒或更好的RMS时钟抖动,才能实现同样的70 dB SNR性能。

ADC的噪声频谱密度可简单定义为ADC的满量程信号功率减去噪声功率,然后分布在1 Hz带宽单位增量上。 FFT采样深度变化并不影响ADC的噪声频谱密度。 它只会将噪声分布在不同的单位频率带宽上。

噪声形状可能会有所不同,具体取决于ADC架构以及是否使用数字滤波器来滤除带外噪声。 对于带宽远大于系统要求的奈奎斯特速率ADC,处理增益可提高目标带宽内的动态范围。

模数转换器相关文章:模数转换器工作原理

评论