便携式设备中的电源效率

高PSRR带隙电压参考电路

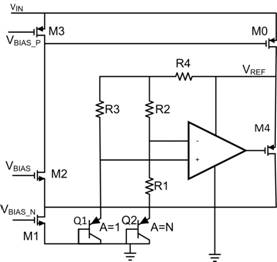

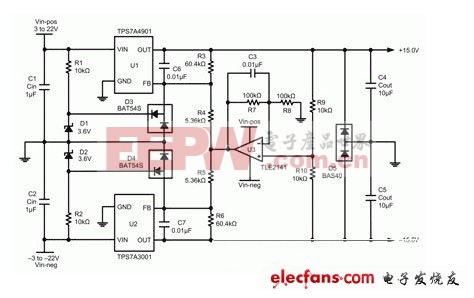

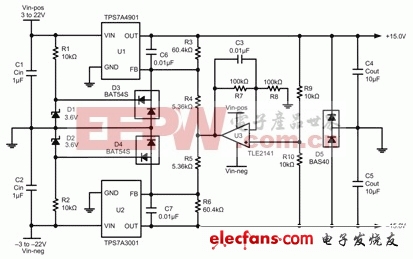

本文引用地址:http://www.eepw.com.cn/article/264576.htm由于上述传统电压参考架构的所有缺点,我们建议采用改进的电压参考,它是带隙电压参考与低压降稳压器的整合解决方案(图6)。

图6.带隙电压参考结合低压降稳压器的方框图

该示例中的输出电压可由公式8确定:

VREF节点既是带隙参考的输出节点,同时也是带隙核心电路的电源线。这有助于我们通过 LDO保护带隙核心电路免受电源电压纹波影响。

要获得小静态电流,电阻器 R1、R2、R3和R4的值就会比较大,推荐电路的电阻为8MΩ。这可使通过 Q1和Q2的电流降低至 40nA。推荐架构的整体静态电流为250nA。除此之外,我们还可采用一款静态电流为100nA的偏置电流电源。

偏置电流电路

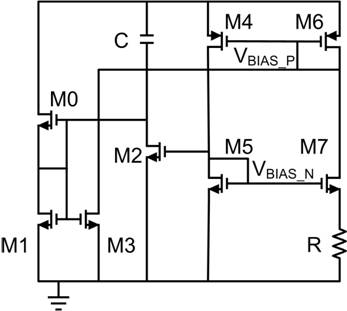

所推荐的偏置电流电路基于一种著名的电路结构(如图7所示),在参考文献5[5]中有详细介绍。

在该电路中,两个N型晶体管M5和M7构成第一个增益为S7/S5 的电流镜,而两个P型晶体管M4和M6 则构成第二个增益为S4/S6 的电流镜,其中S4、S5、S6和S7是相应晶体管的面积。

偏置发生器通常不需要特别启动电路,这可减少静态电流和占用面积。如果电流足够小,电阻R 就可以忽略。由M5/M7和M4/M6构成的两个电流镜可互连成一个闭环。

该环路增益大于单位增益,因此两个分支中的电流都会增大,直至达到均衡为止。这将由电阻R的压降定义,可表示为公式9:

图7.具有动态启动电流的偏置生成器

要加快启动速度并避免可能的漏电影响,可使用一款附加启动电路。晶体管M0 可作为具有极大电阻的横向双极性 NPN晶体管使用,其可最大限度地降低启动电流。电容器 C 不仅可在电路加电时提供快速瞬态启动,而且还可防止启动电路发生振荡。在启动之后,电路由晶体管M2阻断。偏置模块的偏置电流是40nA。总流耗是 80nA。

验证结果

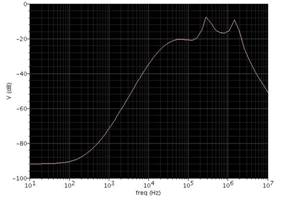

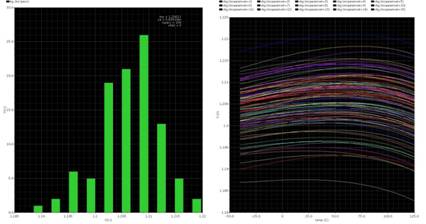

所推荐带隙参考不仅可用于超低噪声、高PSRR的低压降稳压器,而且还可采用CMOS 9T5V 技术实施。PSRR值如图8所示,输出电压精度的蒙特卡洛温度变化仿真结果如图9所示。测量结果请参见表1。

图8.电压参考源的PSRR

图9.输出电压精度

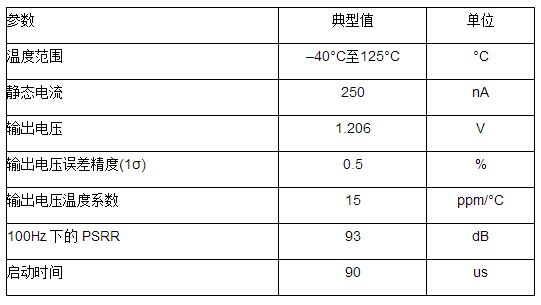

表1.测量数据

总结

我们不仅介绍了采用 CMOS9T5V 0.18µm工艺实施的、高PSRR 的极低功耗带隙电压参考,而且还详细介绍了最大限度降低功耗和最大限度提高PSRR的设计条件。将带隙电压参考与低压降稳压器相结合,可在100Hz下获得93dB的高PSRR。该电路的最大静态电流仅为250nA,是超低功耗应用最具吸引力的选择。

参考文献

J. Guo和K. N. Leung,《采用 90 纳米 CMOS工艺技术实施的、无输出电容器的小型 6uWLDO》,摘自《IEEE固态电路杂志》2010年9月第 48卷第 9 号;

Blakiewicz, G.,《支持更快时间响应的CMOS低压降稳压器》,摘自《2011年第18届国际大会会议记录 — 集成电路与系统混合设计 (MIXDES)》2011年6月16 ~ 18 日第 ××卷第 ×× 号的第 279 页 ~ 282 页;

P. Hazucha、T. Karnik、B. A. Bloecher、C. Parsons、D. Finan 和 S. Borkar,《支持超快负载调节的小型线性稳压器》,摘自《IEEE固态电路杂志》2005 年 4 月第 45 卷第 4 号;

S. Strik,《带隙电压参考:误差及其最小化方法》,摘自《BEC 2006会议记录》2006年10月2日第 123 页 ~ 126页;

E. Vittoz 与 J. Fellrath,《基于弱反向工作的CMOS模拟集成电路》,摘自《IEEE固态电路杂志》1977年6月SC-12卷第 3 号;

如欲了解有关LDO的更多详情,敬请访问:www.ti.com/ldo-ca。

电容器相关文章:电容器原理

评论